# **UNIVERSITY OF WEST ATTICA**

# SCHOOL OF ENGINEERING DEPARTMENT OF INFORMATICS AND COMPUTER ENGINEERING

# Master of Science in Science and Technology of Informatics and Computers

**MASTER THESIS**

Beyond 400G A Preliminary Study of the 800Gb/s and 1.6Tb/s Technologies

> Dimitrios E. Filippou S.N. 20038

Lecturer: Dr. Antonios Bogris, Professor

#### **MASTER THESIS**

#### Beyond 400G A Preliminary Study of the 800Gb/s and 1.6Tb/s Technologies

#### Dimitrios E. Filippou S.N. 20038

Lecturer:

**Dr. Antonios Bogris**

**Examinations Committee:**

Panagiotis Karkazis, Associate Professor Nikolaos Miridakis, Associate Professor

Examinations Date 20/12/2022

### ΔΗΛΩΣΗ ΣΥΓΓΡΑΦΕΑ ΜΕΤΑΠΤΥΧΙΑΚΗΣ ΕΡΓΑΣΙΑΣ

Ο κάτωθι υπογεγραμμένος Δημήτριος Φιλίππου του Ευθυμίου, με αριθμό μητρώου MCSE20038 φοιτητής του Προγράμματος Μεταπτυχιακών Σπουδών «Επιστήμη και Τεχνολογία της Πληροφορική και των Υπολογιστών» του Τμήματος Μηχανικών Πληροφορικής και Υπολογιστών της Σχολής Μηχανικών του Πανεπιστημίου Δυτικής Αττικής, δηλώνω ότι:

«Είμαι συγγραφέας αυτής της μεταπτυχιακής εργασίας και ότι κάθε βοήθεια την οποία είχα για την προετοιμασία της, είναι πλήρως αναγνωρισμένη και αναφέρεται στην εργασία. Επίσης, οι όποιες πηγές από τις οποίες έκανα χρήση δεδομένων, ιδεών ή λέξεων, είτε ακριβώς είτε παραφρασμένες, αναφέρονται στο σύνολό τους, με πλήρη αναφορά στους συγγραφείς, τον εκδοτικό οίκο ή το περιοδικό, συμπεριλαμβανομένων και των πηγών που ενδεχομένως χρησιμοποιήθηκαν από το διαδίκτυο. Επίσης, βεβαιώνω ότι αυτή η εργασία έχει συγγραφεί από μένα αποκλειστικά και αποτελεί προϊόν πνευματικής ιδιοκτησίας τόσο δικής μου, όσο και του Ιδρύματος.

Παράβαση της ανωτέρω ακαδημαϊκής μου ευθύνης αποτελεί ουσιώδη λόγο για την ανάκληση του πτυχίου μου».

Επιθυμώ την απαγόρευση πρόσβασης στο πλήρες κείμενο της εργασίας μου εκτός από ακαδημαϊκούς σκοπούς και έπειτα από αίτηση μου στη Βιβλιοθήκη και έγκριση του επιβλέποντα καθηγητή.

Ο Δηλών

## ΕΥΧΑΡΙΣΤΙΕΣ

Η παρούσα διπλωματική εργασία ολοκληρώθηκε μετά από επίμονες προσπάθειες, σε ένα ενδιαφέρον γνωστικό αντικείμενο, όπως αυτό των σύγχρονων τεχνολογιών μετάδοσης πληροφορίας και ειδικότερα στον κόσμο του Ethernet (IEEE 802.3). Την προσπάθειά μου αυτή υποστήριξε ο επιβλέπων καθηγητής μου, τον οποίο θα ήθελα από καρδίας να ευχαριστήσω.

Ακόμα θα ήθελα να ευχαριστήσω τον εξαίρετο συνάδελφο και Distinguished Engineer της εταιρείας CISCO SYSTEMS, Silicon Valley, κύριο Peter Jones για την πολύτιμη βοήθεια και καθοδήγηση στον κόσμο της τυποποίησης και των πρωτοκόλλων της IEEE.

Επιπλέον, θα ήθελα να ευχαριστήσω την οικογένειά μου, τη σύζυγο και τον γιό μου για την αμέριστη στήριξη τους στην προσπάθεια μου να ολοκληρώσω επιτυχώς τις μεταπτυχιακές μου σπουδές.

## ΠΕΡΙΛΗΨΗ

Η παρούσα διπλωματική εργασία ασχολείται με την ανάπτυξη αλγορίθμων συγγραφής διπλωματικών εργασιών. Σε αυτό το πεδίο έχουν αναπτυχθεί ιστορικά αρκετοί αλγόριθμοι, κάθε ένας από τους οποίους έχει ορισμένα πλεονεκτήματα και μειονεκτήματα. Ο προτεινόμενος αλγόριθμος λαμβάνει υπ' όψη του τις απαιτήσεις του Τμήματος και αναλαμβάνει να παρουσιάσει διπλωματικές εργασίες οι οποίες να παρουσιάζουν ομοιογένεια και να μην προκαλούν το Γραμματέα ο οποίος θα προσπαθήσει να τις ταξινομήσει στη Βιβλιοθήκη του τμήματος.

Η παρούσα διπλωματική εργασία αποτελεί μια προκαταρκτική μελέτη των τεχνολογιών Ethernet στα 800Gb/s και 1.6Tb/s ως αποτέλεσμα των δραστηριοτήτων της Ομάδας Εργασίας IEEE 802.3 Beyond 400Gb/s Ethernet Task Force (B400G TF), η οποία ιδρύθηκε τον Ιανουάριο του 2021. Οι εργασίες της IEEE B400G TF βρίσκονται σε προκαταρκτικό στάδιο και βασίζονται στην τυπική σειρά προτύπων IEEE Std 802.3. Η IEEE B400G TF ψήφισε τον Νοέμβριο του 2021 το επερχόμενο πρότυπο IEEE P802.3df, το οποίο παρέχει μια αρχιτεκτονική ικανή να υποστηρίξει το Ethernet στα 800Gb/s και 1,6Tb/s, ενώ αναπτύσσει προδιαγραφές Φυσικού Επιπέδου (PHY) για την επικοινωνία σε οπισθεπίπεδα, καλωδιώσεις χαλκού, πολύτροπης και μονότροπης οπτικής ίνας και χρησιμοποιεί την εργασία αυτή για να καθορίσει τις προδιαγραφές των παράγωγων φυσικών επιπέδων και των παραμέτρων διαχείρισης για τη μεταφορά πλαισίων Ethernet στα 100Gb/s, 200Gb/s και 400Gb/s.

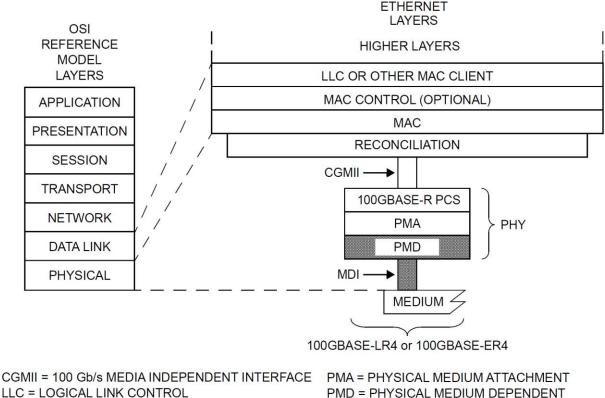

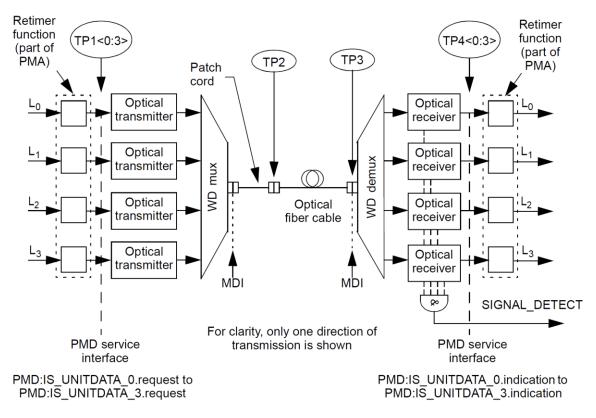

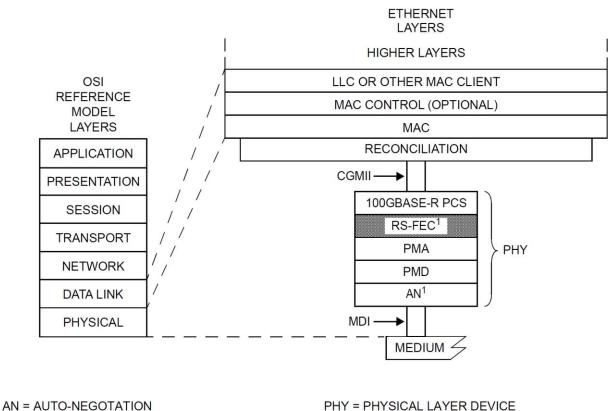

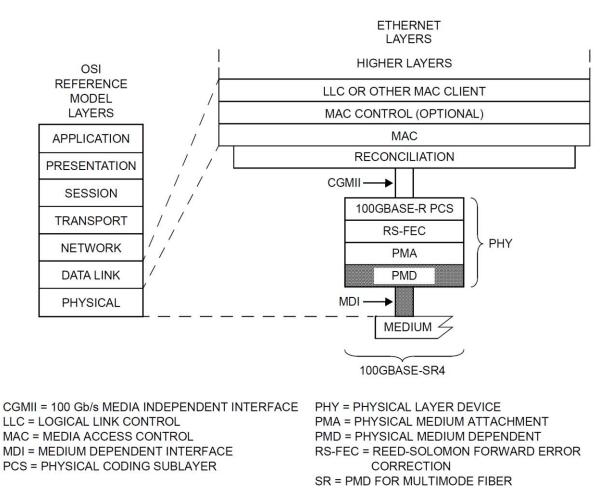

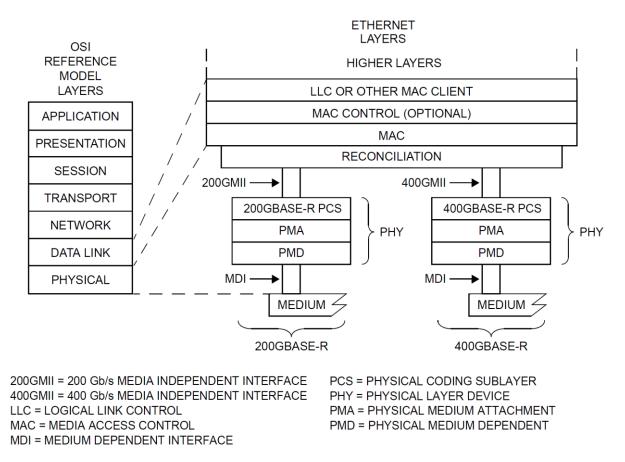

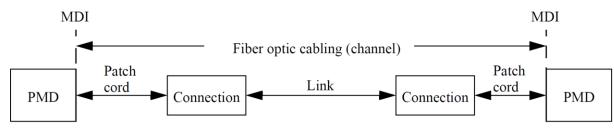

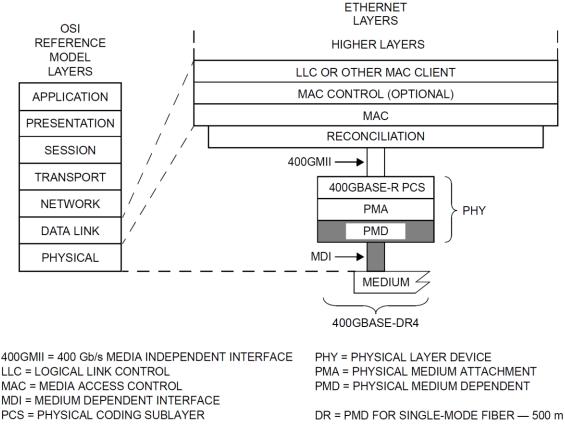

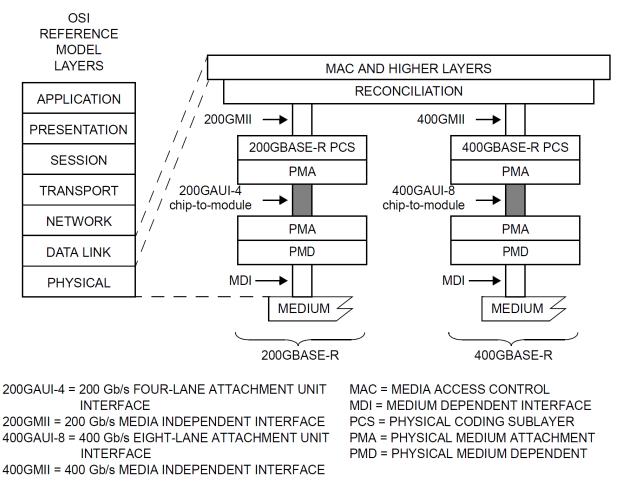

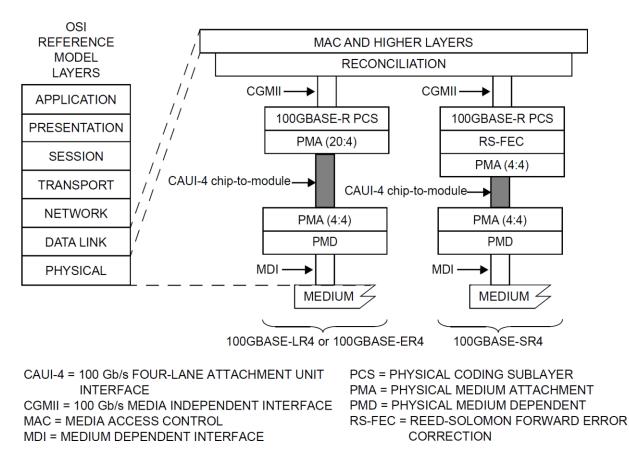

Τα τρία πρώτα κεφάλαια παρούσας διπλωματικής εργασίας παρέχουν μια επισκόπηση της αρχιτεκτονικής των IEEE 802.3 προτύπων, σχετικά με τα 100Gb/s, 200Gb/s και 400Gb/s Ethernet. Η αρχιτεκτονική των IEEE 802.3 προτύπων έχει σχέση με το ISO/IEC μοντέλο αναφοράς διασύνδεσης ανοικτών συστημάτων (OSI), ξεκινώντας από το επίπεδο Ελέγχου του Μέσου Πρόσβασης (MAC) έως το PHY, το οποίο αποτελείται από τρία υποστρώματα και έχει πρόσβαση στο μέσο μετάδοσης. Τα κεφάλαια αυτά δίνουν την ευκαιρία να κατανοήσουμε τις απαιτήσεις και τις προδιαγραφές της σειράς των IEEE 802.3 προτύπων, που θα αποτελέσουν τον πρόδρομο ανάπτυξης των επερχόμενων προτύπων IEEE P802.3df και IEEE P802.3dj.

Το τέταρτο κεφάλαιο παρέχει τις αρχιτεκτονικές προοπτικές για την ανάπτυξη των IEEE P802.3df και IEEE P802.3dj, μέσω των προτάσεων που παραδόθηκαν από τα μέλη της IEEE B400G TF. Οι προτάσεις αυτές αποτελούν μέρος της έρευνας της παρούσας διπλωματικής εργασίας και των τελευταίων εξελίξεων στην τεχνολογία του Ethernet. Η δομή του κεφαλαίου αυτού ακολουθεί τη μορφή της τυπικής σειράς των IEEE 802.3 προτύπων, παρέχει ανάλυση βάσει του εκάστοτε επιπέδου και δίνει την ευκαιρία για μια ολιστική άποψη των επερχόμενων προοπτικών.

Τα παραρτήματα Α έως Μ παρατίθενται στην παρούσα διπλωματική εργασία για ενημερωτικούς σκοπούς, καθώς αποτελούν μέρος των ΙΕΕΕ 802.3 προτύπων.

### ABSTRACT

This paper provides a preliminary study of 800Gb/s and 1.6Tb/s Ethernet technologies as a result of the activities of the IEEE 802.3 Beyond 400Gb/s Ethernet Task Force (B400G TF), which was established in January 2021. The works of IEEE B400G TF are in preliminary level and are based on the IEEE Std 802.3 standard series. IEEE B400G TF voted in November 2021 the upcoming IEEE P802.3df standard, which provides an architecture capable of supporting both 800Gb/s and 1.6Tb/s Ethernet, while producing Physical Layer (PHY) specifications for communication across backplanes, copper cabling, multimode and single-mode fiber and use this work to define derivative physical layer specifications and management parameters for the transfer of Ethernet format frames at 100Gb/s, 200Gb/s and 400Gb/s.

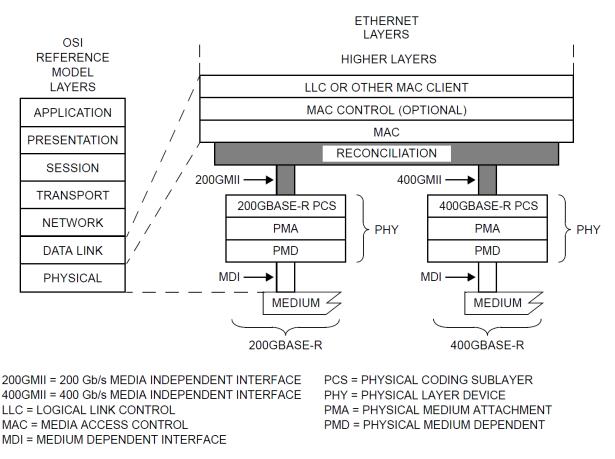

The first three chapters of this study provide an overview of the IEEE 802.3 architecture, regarding 100Gb/s, 200Gb/s and 400Gb/s Ethernet. IEEE 802.3 architecture has a relationship to the ISO/IEC Open System Interconnection (OSI) reference model, starting from the Media Access Control (MAC) layer to the PHY, which consists of three sublayers and has access to the medium. These chapters give the opportunity to understand the requirements and specifications of IEEE 802.3 standard series, which will be the development precursor of the upcoming IEEE P802.3df and IEEE P802.3dj standards.

The fourth chapter provides the architectural perspectives for the development of IEEE P802.3df and IEEE P802.3dj, through the proposals delivered from the IEEE B400G TF members. These proposals are part of the research and the latest developments in Ethernet technology. The structure of this chapter follows the format

of the IEEE 802.3 standard series, provides a layer-based analysis, and gives the opportunity for a holistic view of the upcoming perspectives.

Annexes A to M are included in this paper for informative purposes, since they are part of the IEEE 802.3 standards.

**SCIENTIFIC DOMAIN:** IEEE Standards for Ethernet, Media Access Control Parameters, Physical Layers, and Management Parameters

**KEYWORDS:** 100Gb/s Ethernet, 100CGMII, 100GAUI, 100GBASE-ER4, 100GBASE-R, 100GBASE-LR4, 100GBASE-SR10, 200Gb/s Ethernet, 200GAUI-4, 200GAUI-8, 200GBASE-DR4, 200GBASE-FR4, 200GBASE-LR4, 200GBASE-DR4, 200GBASE-FR8, 400GBASE-LR8, 400GBASE-SR16, 400GBASE-R, 400GBASE-FR8, 400GBASE-LR8, 400GBASE-SR16, 400GBASE-R, 400GMII, 400GXS, 800Gb/s Ethernet, 1.6Tb/s Ethernet, EEE, Energy Efficient Ethernet, Ethernet, FEC, Forward Error Correction, IEEE 802.3, IEEE 802.3bs, IEEE 802.3df, IEEE 802.3dj, MDI, Medium Dependent Interface, MMF, MultiMode Fiber, PAM4, PCS, Physical Coding Sublayer, PMA, Physical Medium Dependent, PMD, Physical Medium Dependent sublayer, RS, Reconciliation Sublayer, SMF, Single Mode Fiber.

# Contents

| 1             | Intr                                                         | oduo                                                        | ction                                                                  |

|---------------|--------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------|

| 2             | IEE                                                          | E 80                                                        | 02.3™ - 2018 Ethernet Standard34                                       |

| 2             | .1                                                           | Ме                                                          | dia Access Control (MAC) Sublayer34                                    |

|               | 2.1                                                          | .1                                                          | MAC Control Sublayer Architecture                                      |

|               | 2.1                                                          | .2                                                          | MAC Control Frame Format                                               |

| 2             | .2                                                           | Arc                                                         | hitectural Perspectives of 100Gb/s Ethernet                            |

|               | 2.2                                                          | .1                                                          | Delay constraints                                                      |

|               | 2.2                                                          | .2                                                          | Skew constraints                                                       |

| 2             | .3                                                           | Red                                                         | conciliation Sublayer (RS) and Media Independent Interface for 100Gb/s |

| ope           | eratio                                                       | on (C                                                       | CGMII)                                                                 |

|               | 2.3                                                          | .1                                                          | Delay constraints                                                      |

| 2             | .4                                                           | Phy                                                         | vsical Coding Sublayer (PCS) for 64B/66B, type 100GBASE-R50            |

| 2             | .5                                                           | Phy                                                         | vsical Medium Attachment (PMA) sublayer, type 100GBASE-R 52            |

|               |                                                              |                                                             |                                                                        |

|               | .6                                                           |                                                             | vsical Medium Dependent (PMD) sublayer and medium, type                |

|               |                                                              |                                                             | vsical Medium Dependent (PMD) sublayer and medium, type<br>-SR10       |

|               |                                                              | ASE                                                         |                                                                        |

|               | )GB/                                                         | ASE                                                         | -SR10                                                                  |

|               | )GB/<br>2.6                                                  | ASE<br>.1<br>.2                                             | -SR10                                                                  |

|               | )GB/<br>2.6<br>2.6                                           | ASE<br>.1<br>.2<br>.3                                       | -SR10                                                                  |

| 100           | )GB,<br>2.6<br>2.6<br>2.6<br>2.6                             | ASE<br>.1<br>.2<br>.3                                       | -SR10                                                                  |

| 100           | )GB,<br>2.6<br>2.6<br>2.6<br>2.6                             | ASE<br>.1<br>.2<br>.3<br>.4<br>ods                          | -SR10                                                                  |

| 100           | )GB,<br>2.6<br>2.6<br>2.6<br>2.6<br>neth                     | ASE<br>.1<br>.2<br>.3<br>.4<br>ods<br>.5                    | -SR10                                                                  |

| 100           | )GB,<br>2.6<br>2.6<br>2.6<br>2.6<br>nethe<br>2.6             | ASE<br>.1<br>.2<br>.3<br>.4<br>ods<br>.5<br>.6              | -SR10                                                                  |

| 100<br>n      | )GB,<br>2.6<br>2.6<br>2.6<br>2.6<br>2.6<br>2.6<br>2.6        | ASE<br>.1<br>.2<br>.3<br>.4<br>ods<br>.5<br>.6<br>.7        | -SR10                                                                  |

| 100<br>m<br>2 | )GB,<br>2.6<br>2.6<br>2.6<br>2.6<br>2.6<br>2.6<br>2.6<br>2.6 | ASE<br>.1<br>.2<br>.3<br>.4<br>ods<br>.5<br>.6<br>.7<br>Phy | -SR10                                                                  |

| 2.7.2        | Wavelength-division-multiplexed lane assignments                       |

|--------------|------------------------------------------------------------------------|

| 2.7.3<br>ER4 | PMD to MDI optical specifications for 100GBASE-LR4 and 100GBASE-<br>89 |

| 2.7.4        | Definition of optical parameters and measurement methods93             |

| 2.7.5        | Safety, installation, environment, and labeling                        |

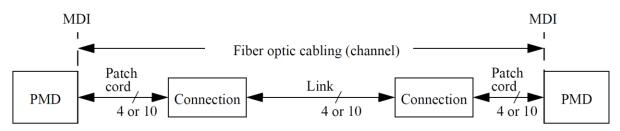

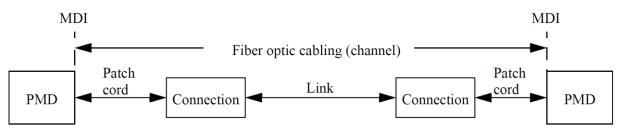

| 2.7.6        | Fiber optic cabling model99                                            |

| 2.7.7        | Characteristics of the fiber optic cabling (channel) 100               |

|              | eed-Solomon Forward Error Correction (RS-FEC) sublayer for<br>E-R PHYs |

| 2.8.1        | FEC service interface 102                                              |

| 2.8.2        | PMA compatibility104                                                   |

| 2.8.3        | Delay constraints104                                                   |

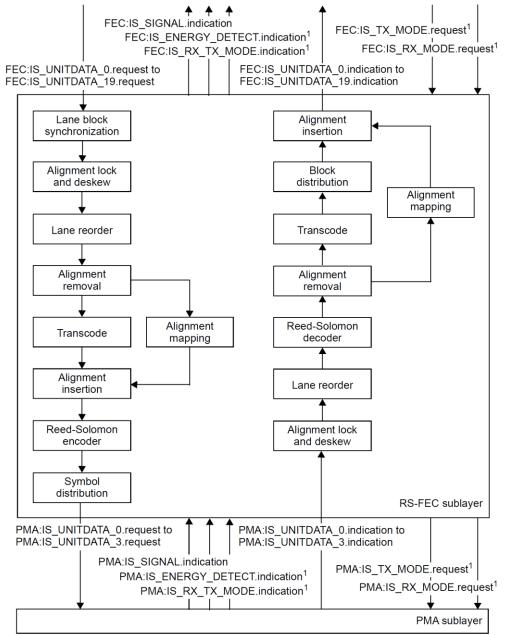

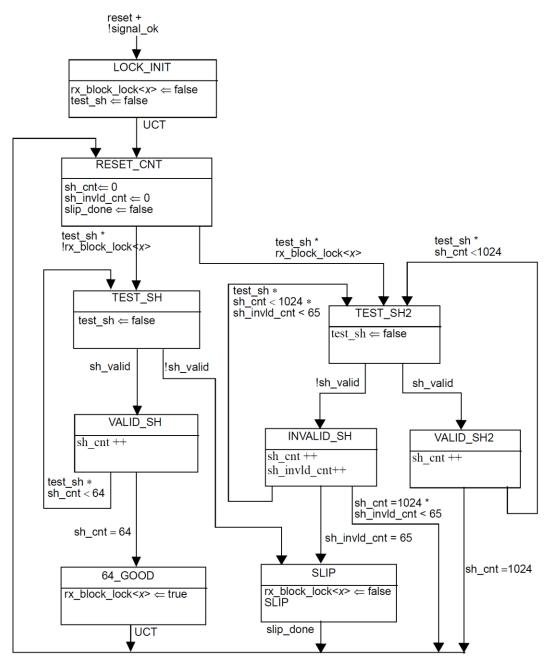

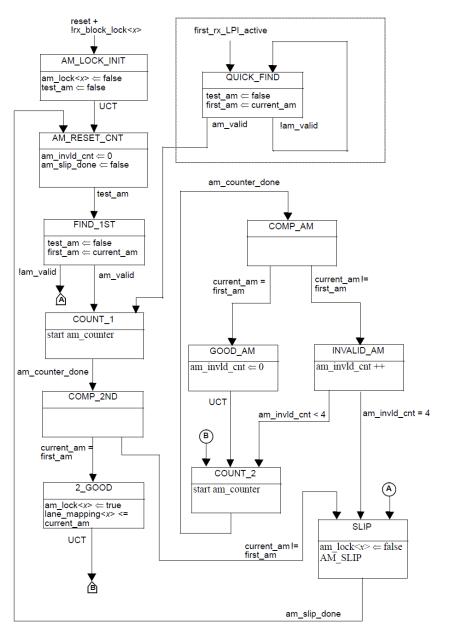

| 2.8.4        | Functions within the RS-FEC sublayer104                                |

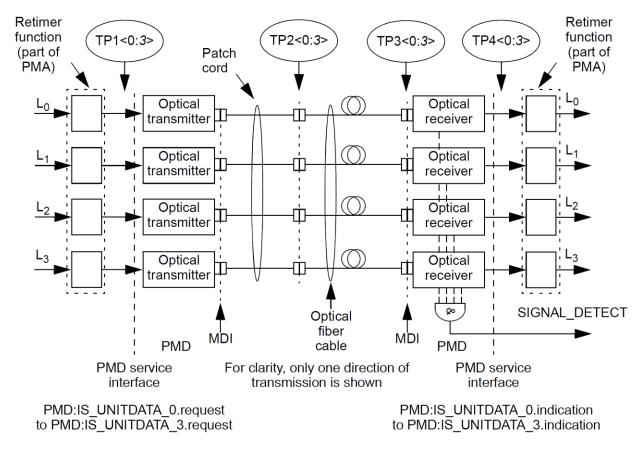

|              | hysical Medium Dependent (PMD) sublayer and medium, type<br>E-SR4      |

| 2.9.1        | PMD functional specifications126                                       |

| 2.9.2        | Lane assignments 129                                                   |

| 2.9.3        | PMD to MDI optical specifications for 100GBASE-SR4 129                 |

| 2.9.4        | Definition of optical parameters and measurement methods 131           |

| 2.9.5        | Safety, installation, environment, and labeling143                     |

| 2.9.6        | Fiber optic cabling model 143                                          |

| 2.9.7        | Characteristics of the fiber optic cabling (channel) 144               |

| 3 Archi      | ectural Perspectives of 200Gb/s and 400Gb/s Ethernet                   |

| 3.1 N        | ledia Access Control (MAC)149                                          |

| 3.1.1        | MAC Service Specifications149                                          |

| 3.1.2        | MAC Frame and Packet Specifications                                    |

|              |                                                                        |

| 3.1.3        | Delay constraints                                                      |

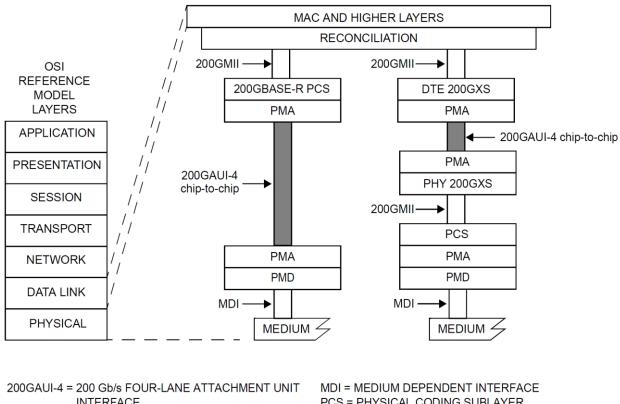

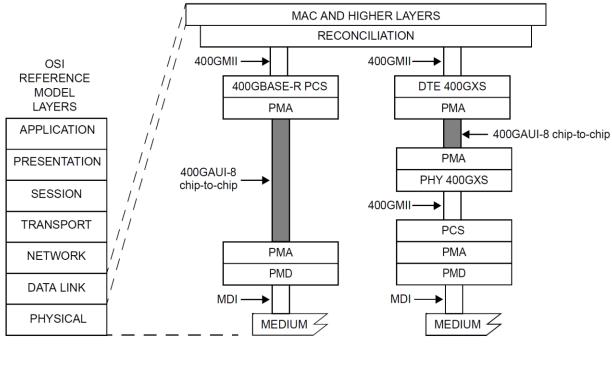

| 3.2 Reconciliation Sublayer (RS) and Media Independent Interface (MII) 157 |

|----------------------------------------------------------------------------|

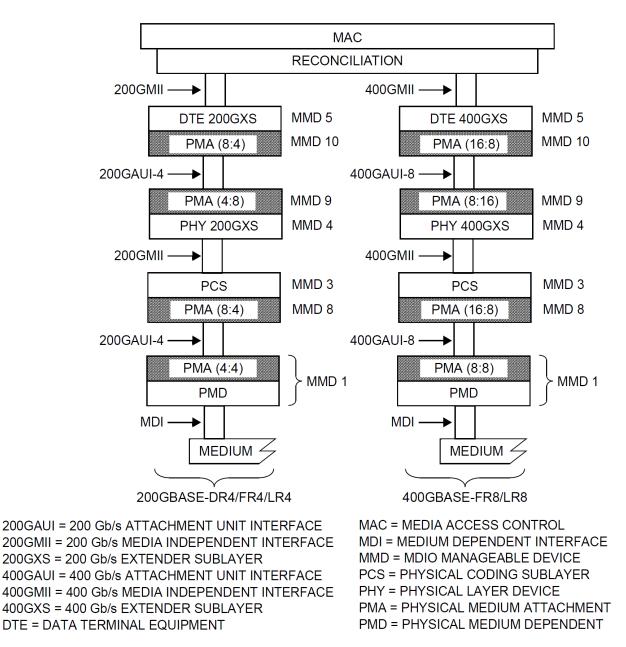

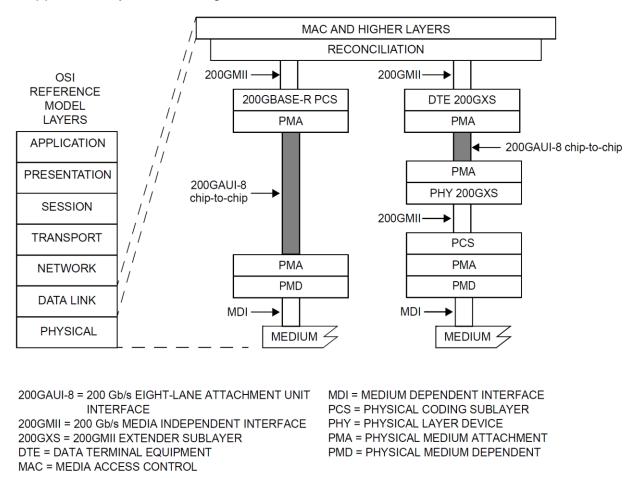

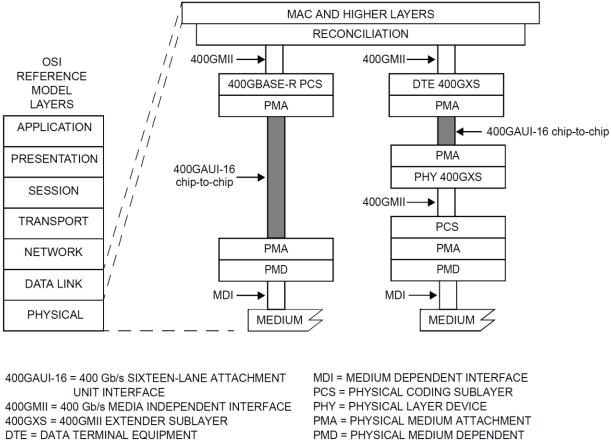

| 3.3 200GMII Extender, 400GMII Extender, 200GMII Extender Sublayer          |

| (200GXS), and 400GMII Extender Sublayer (400GXS) 159                       |

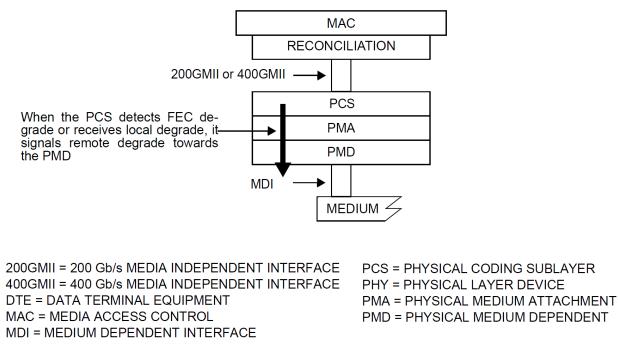

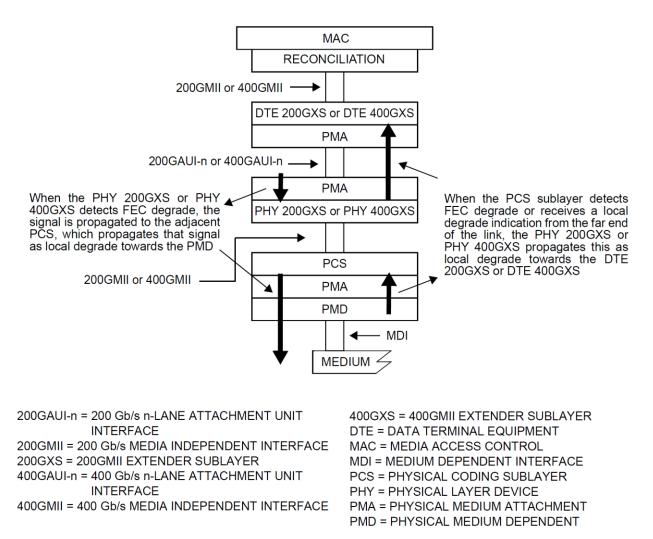

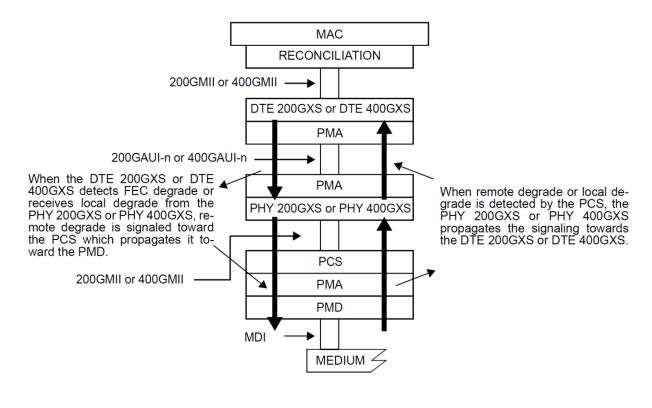

| 3.3.1 FEC Degrade                                                          |

| 3.4 Physical Coding Sublayer (PCS) for 64B/66B, type 200GBASE-R and        |

| 400GBASE-R                                                                 |

| 3.5 Physical Medium Attachment (PMA) sublayer, type 200GBASE-R and         |

| 400GBASE-R                                                                 |

| 3.6 Physical Medium Dependent (PMD) sublayer and medium, type              |

| 200GBASE-DR4                                                               |

| 3.6.1 PMD Functional Specifications172                                     |

| 3.6.2 Lane assignments 174                                                 |

| 3.6.3 PMD to MDI optical specifications for 200GBASE-DR4 174               |

| 3.6.4 Definition of optical parameters and measurements methods 176        |

| 3.6.5 Safety, installation, environment, and labeling                      |

| 3.6.6 Fiber optic cabling model                                            |

| 3.6.7 Characteristics of the fiber optic cabling (channel)                 |

| 3.7 Physical Medium Dependent (PMD) sublayer and medium, type              |

| 200GBASE-FR4, 200GBASE-LR4, 400GBASE-FR8, 400GBASE-LR8                     |

| 3.7.1 PMD Functional Specifications190                                     |

| 3.7.2 Wavelength-division-multiplexing lane assignments                    |

| 3.7.3 PMD to MDI optical specifications for 200GBASE-FR4, 200GBASE-        |

| LR4, 400GBASE-FR8, and 400GBASE-LR8194                                     |

| 3.7.4 Definition of optical parameters and measurements methods 200        |

| 3.7.5 Safety, installation, environment, and labeling                      |

| 3.7.6 Fiber optic cabling model                                            |

| 3.7.7 Characteristics of the fiber optic cabling (channel)                 |

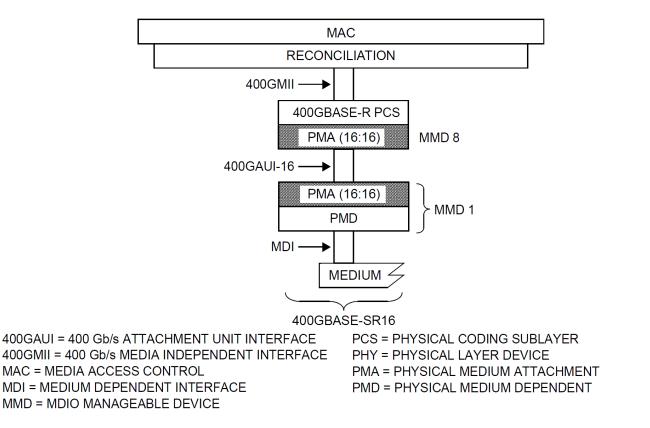

|    | 3.8 |       |          |               | Dependent       |             |            |        |             |       |

|----|-----|-------|----------|---------------|-----------------|-------------|------------|--------|-------------|-------|

| 40 | OGB | ASE   | -SR16    |               |                 |             |            |        |             | 210   |

|    | 3.8 | 5.1   | PMD      | Functiona     | Specificatior   | าร          |            |        |             | 212   |

|    | 3.8 | .2    | Lane     | assignmei     | nts             |             |            |        |             | 215   |

|    | 3.8 | .3    | PMD      | to MDI opt    | tical specifica | tions for   | 400GBASE   | E-SR1  | 6           | 215   |

|    | 3.8 | .4    | Defin    | ition of opt  | ical paramete   | ers and m   | neasureme  | nts me | ethods      | 216   |

|    | 3.8 | .5    | Safet    | y, installati | on, environm    | ent, and    | labeling   |        |             | 217   |

|    | 3.8 | .6    | Fiber    | optic cabli   | ng model        |             |            |        |             | 218   |

|    | 3.8 | .7    | Chara    | acteristics   | of the fiber op | otic cablir | ng (channe | l)     |             | 219   |

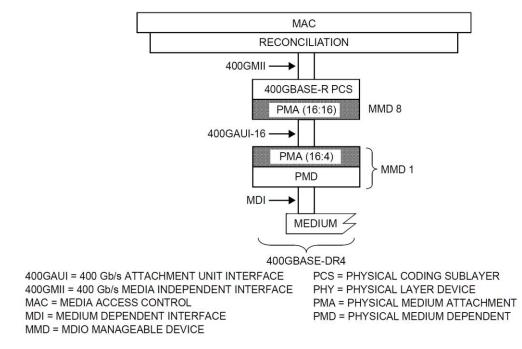

|    | 3.9 | Phy   | /sical   | Medium        | Dependent       | (PMD)       | sublayer   | and    | medium,     | type  |

| 40 | 0GB | ASE   | -DR4 .   |               |                 |             |            |        |             | 221   |

|    | 3.9 | .1    | PMD      | Functiona     | Specificatior   | าร          |            |        |             | 223   |

|    | 3.9 | .2    | Lane     | assignmei     | nts             |             |            |        |             | 226   |

|    | 3.9 | .3    | PMD      | to MDI opt    | tical specifica | tions for   | 400GBASE   | E-DR4  | ·           | 226   |

|    | 3.9 | .4    | Defin    | ition of opt  | ical paramete   | ers and m   | neasureme  | nts me | ethods      | 228   |

|    | 3.9 | .5    | Safet    | y, installati | on, environm    | ent, and    | labeling   |        |             | 232   |

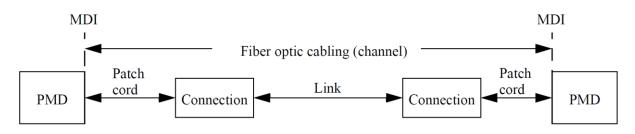

|    | 3.9 | .6    | Fiber    | optic cabli   | ng model        |             |            |        |             | 232   |

|    | 3.9 | .7    | Chara    | acteristics   | of the fiber op | otic cablir | ng (channe | l)     |             | 233   |

| 4  | Arc | chite | ctural I | Perspective   | es of 800Gb/s   | s and 1.6   | Tb/s Ether | net    |             | 237   |

|    | 4.1 | 800   | )Gb/s a  | and 1.6TG     | b/s MAC sub     | layer       |            |        |             | 245   |

|    | 4.2 | Re    | concilia | ation Subla   | ayer (RS) and   | l Media II  | ndependen  | t Unit | (MII)       | 245   |

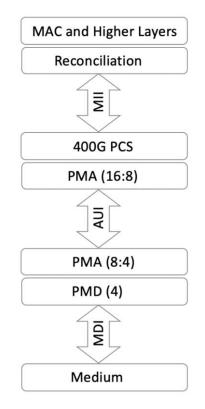

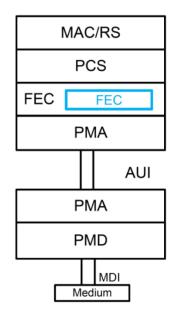

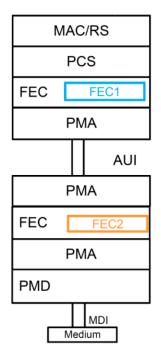

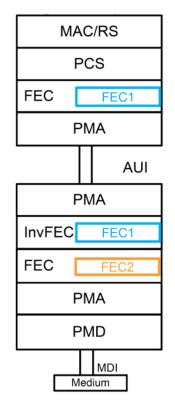

|    | 4.3 | Phy   | /sical ( | Coding Sul    | blayer (PCS)    | and Forv    | vard Error | Correc | ction (FEC) | . 246 |

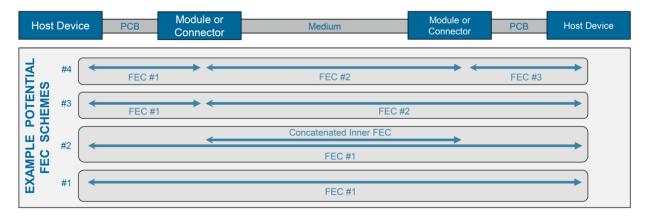

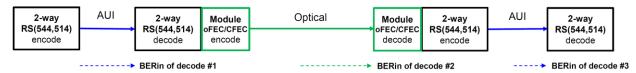

|    | 4.3 | 5.1   | End-t    | o-End FEC     | CScheme         |             |            |        |             | 255   |

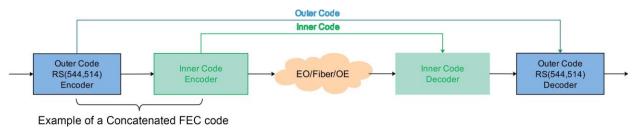

|    | 4.3 | .2    | Enca     | psulated o    | r Concatenate   | ed FEC S    | Scheme     |        |             | 256   |

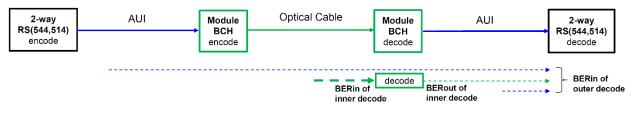

|    | 4.3 | .3    | Seam     | nented FE(    | C Scheme        |             |            |        |             | 261   |

|    | 4.3 |       | Ū        |               | between FEC     |             |            |        |             |       |

|    | 4.4 |       |          |               | tachment (PN    |             |            |        |             |       |

|    | -   |       | ,        |               |                 | ,           | ,          |        |             |       |

| 4.5 Ph | sical Medium Depender | nt (PMD) Sublayer | 271 |

|--------|-----------------------|-------------------|-----|

|--------|-----------------------|-------------------|-----|

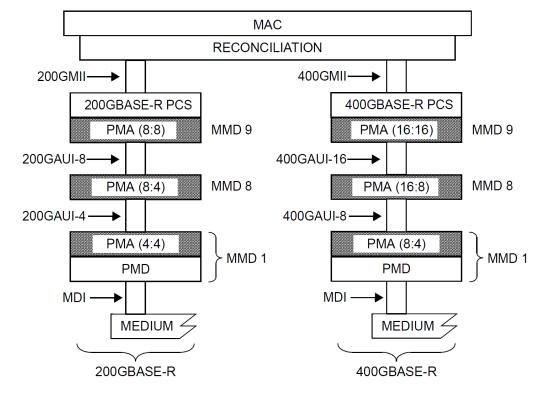

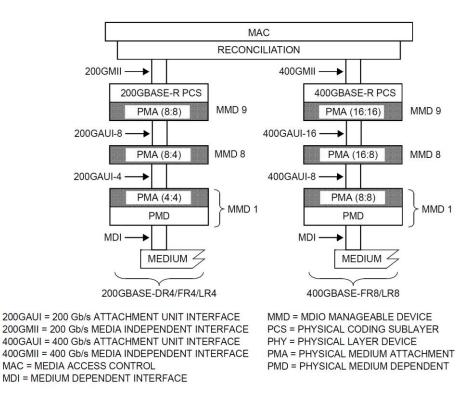

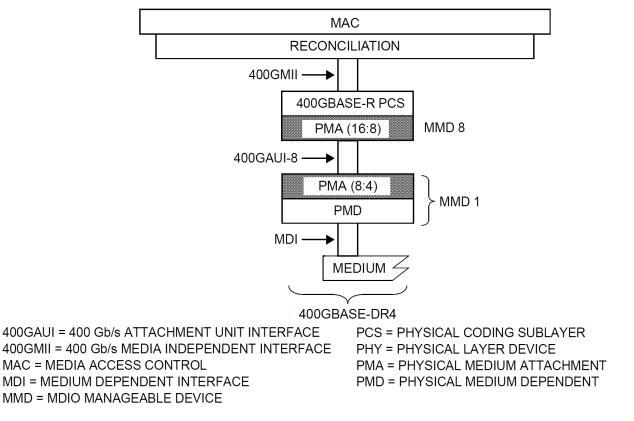

Annex A. 200Gb/s and 400Gb/s PMA sublayer partitioning examples ............273

A.3 Partitioning example supporting 400GBASE-DR4 ...... 275

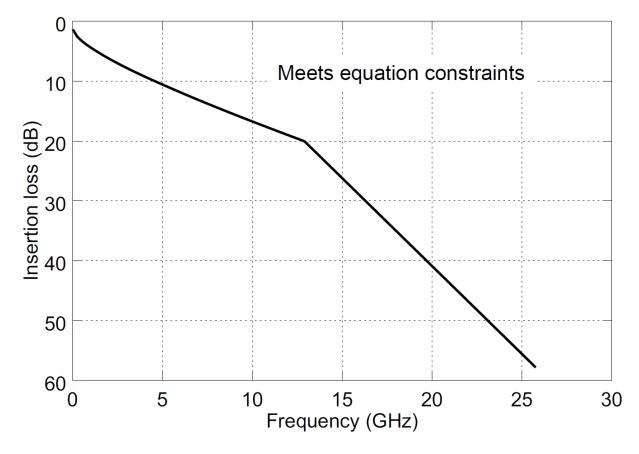

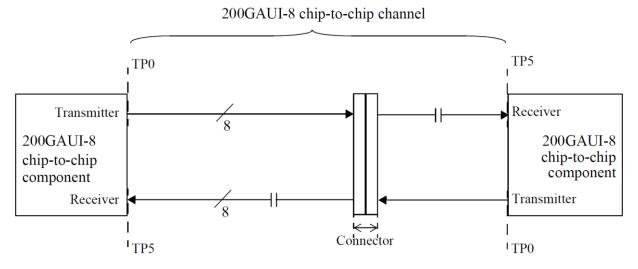

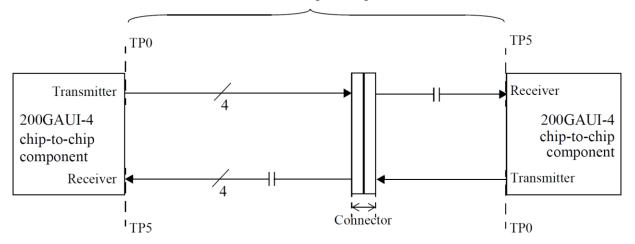

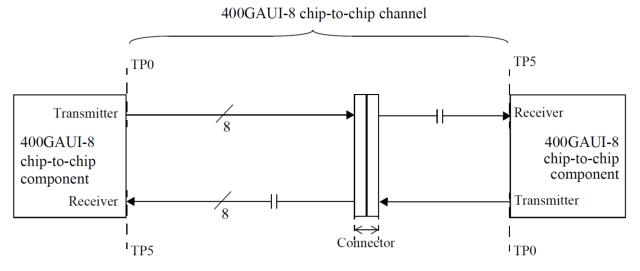

Annex B. Chip-to-chip 200 Gb/s eight-lane Attachment Unit Interface (200GAUI-8 C2C) and 400 Gb/s sixteen-lane Attachment Unit Interface (400GAUI-16 C2C) 278

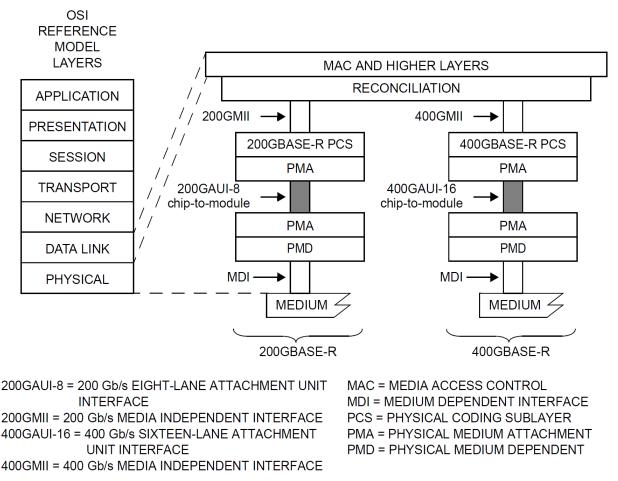

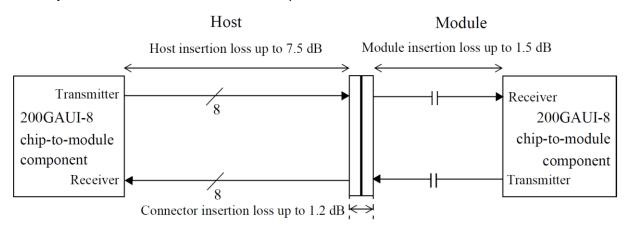

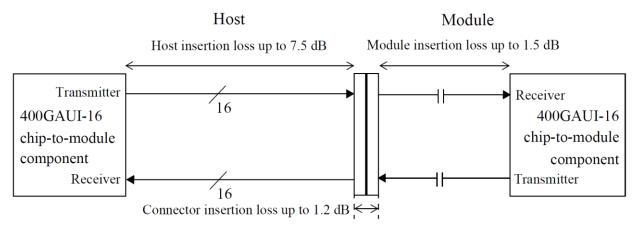

Annex C. Chip-to-module 200 Gb/s eight-lane Attachment Unit Interface (200GAUI-8 C2M) and 400 Gb/s sixteen-lane Attachment Unit Interface (400GAUI-16 C2M) 283

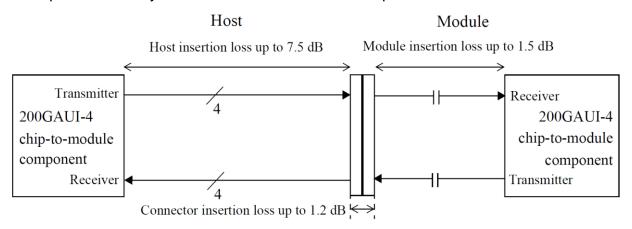

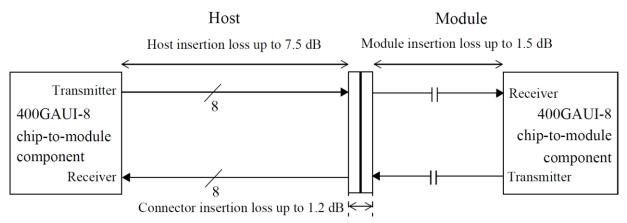

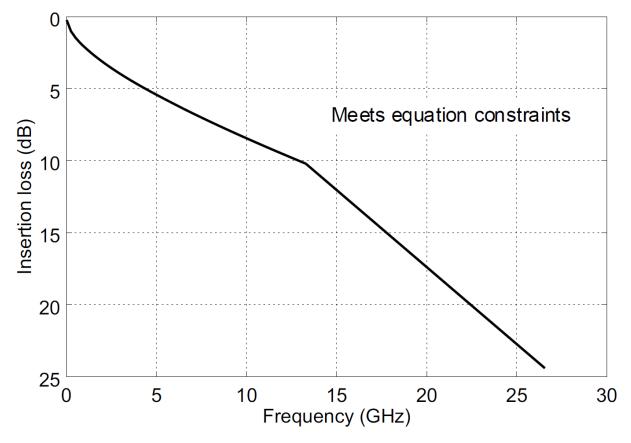

Annex E. Chip-to-module 200 Gb/s four-lane Attachment Unit Interface (200GAUI-4 C2M) and 400 Gb/s eight-lane Attachment Unit Interface (400GAUI-8 C2M) 290

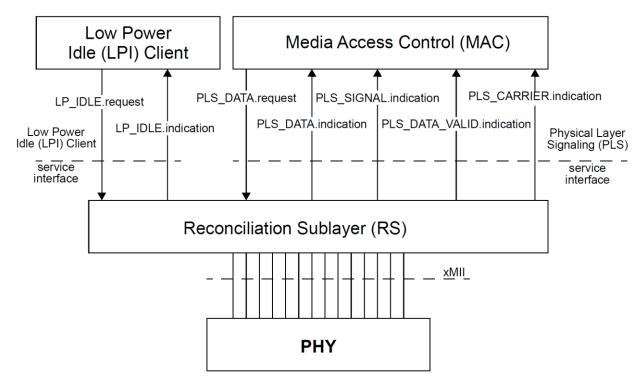

| Annex F.  | Energy-Efficient Ethernet (EEE)                       |  |

|-----------|-------------------------------------------------------|--|

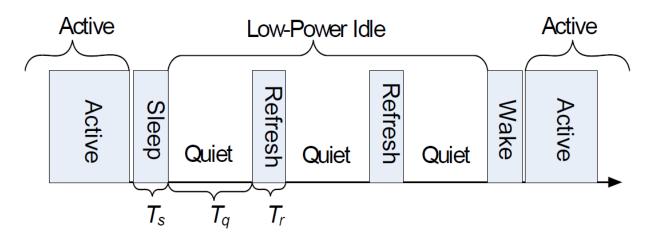

| F.1 LPI S | Signaling                                             |  |

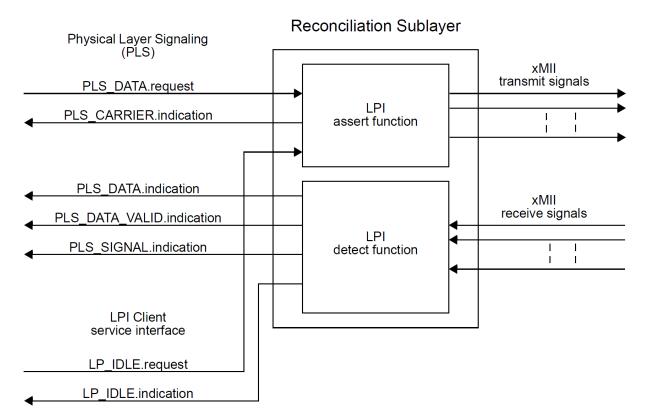

| F.1.1 F   | Reconciliation sublayer service interfaces            |  |

| F.1.2 F   | Reconciliation sublayer operation                     |  |

| F.1.3 F   | PHY LPI transmit operation                            |  |

| F.1.4 F   | PHY LPI receive operation                             |  |

| Annex G.  | MAC Control PAUSE operation                           |  |

| Annex H.  | 100 Gb/s ten-lane Attachment Unit Interface (CAUI-10) |  |

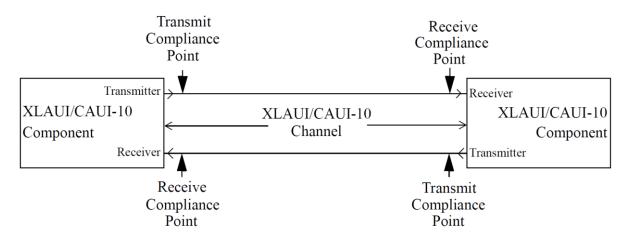

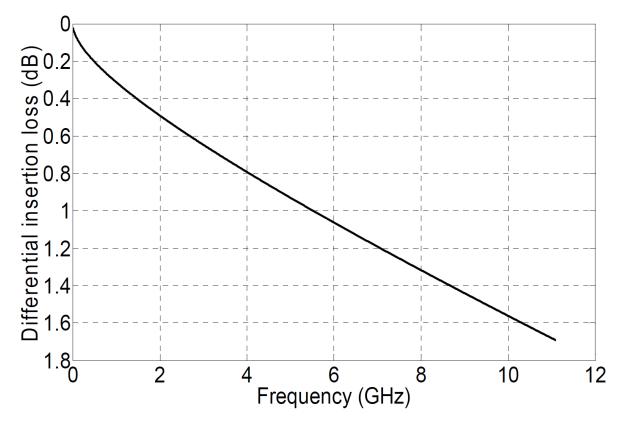

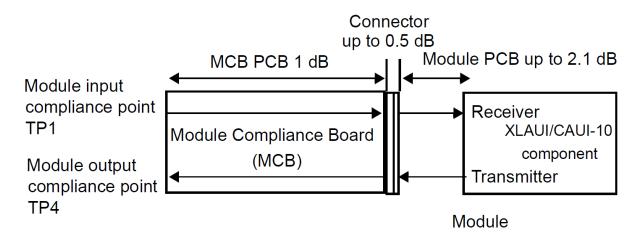

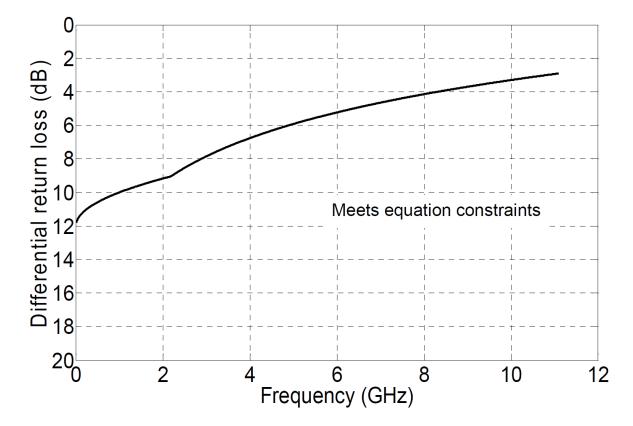

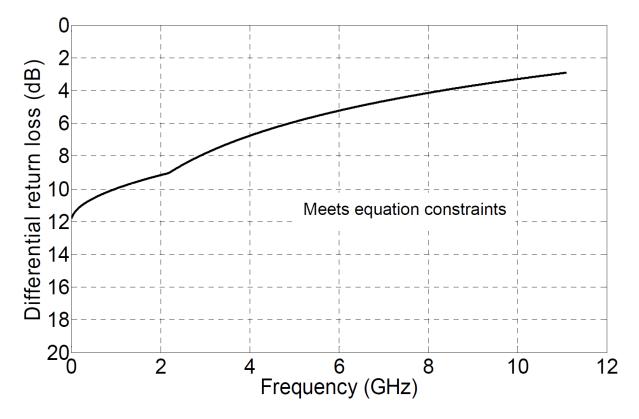

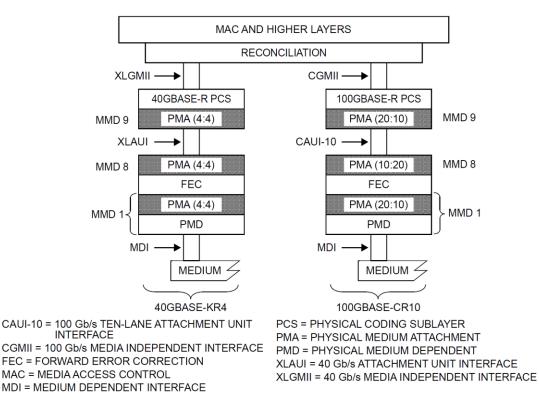

| H.1. CAU  | JI-10 link block diagram                              |  |

| H.1.1.    | Transmitter compliance points                         |  |

| H.1.2.     | Receiver compliance points                                              | 03   |

|------------|-------------------------------------------------------------------------|------|

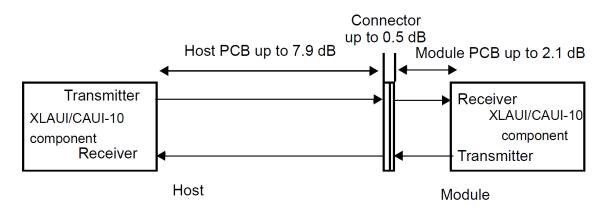

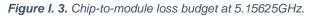

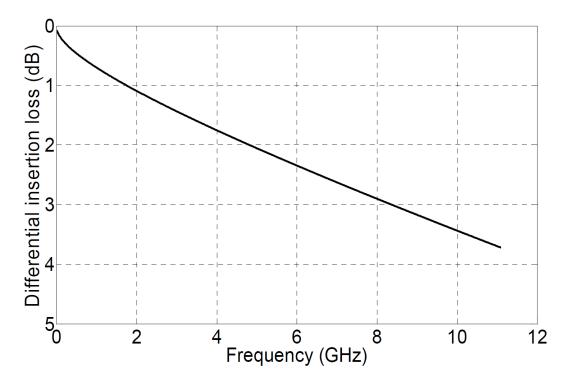

| Annex I.   | Chip-to-module 100Gb/s ten-lane Attachment Unit Interface (CAUI-<br>305 | 10)  |

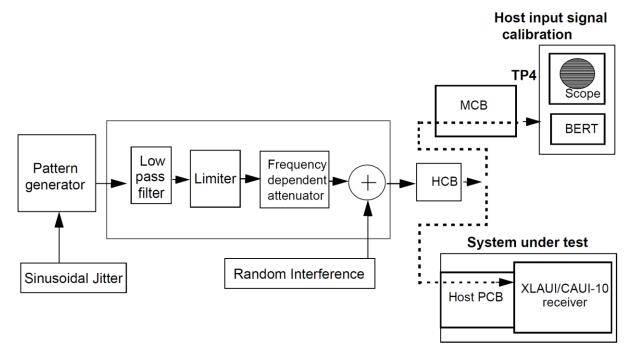

| I.1 Comp   | bliance point specifications for chip-to-module XLAUI/CAUI-103          | 607  |

| I.1.1 M    | lodule specifications                                                   | \$10 |

| I.1.2. ⊦   | lost specifications                                                     | 312  |

| I.1.3. ⊦   | lost input signal tolerance3                                            | \$14 |

| Annex J.   | PMA sublayer partitioning examples3                                     | \$15 |

| J.1. Parti | itioning examples with FEC3                                             | \$15 |

| J.1.1. F   | FEC implemented with PCS 3                                              | \$16 |

| J.1.2. F   | FEC implemented with PMD3                                               | \$16 |

| J.2. Parti | itioning examples with RS-FEC3                                          | 317  |

| J.2.1. S   | Single PMA sublayer with RS-FEC3                                        | 317  |

| J.2.2. \$  | Single CAUI-10 with RS-FEC 3                                            | 317  |

| J.3. Parti | itioning examples without FEC 3                                         | 18   |

| J.3.1. S   | Single PMA sublayer without FEC3                                        | 18   |

| J.3.2. S   | Single XLAUI/CAUI-4 without FEC 3                                       | 18   |

| J.3.3. §   | Separate SERDES for optical module interface                            | 19   |

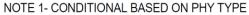

| Annex K.   | Chip-to-chip 100Gb/s four-lane Attachment Unit Interface (CAUI-4)3      | 320  |

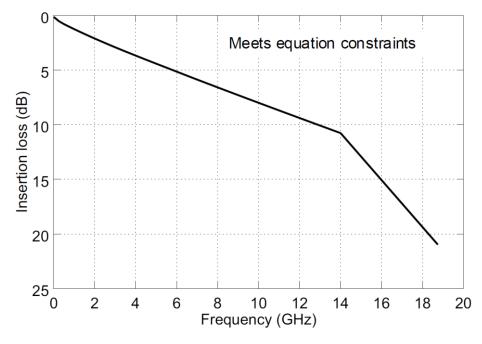

| K.1. CAL   | JI-4 chip-to-chip compliance point definition                           | 322  |

| K.2. CAL   | JI-4 chip-to-chip electrical characteristics                            | 322  |

| K.2.1.     | CAUI-4 transmitter characteristics 3                                    | 322  |

| K.2.2.     | Optional Energy Efficient Ethernet (EEE) operation                      | 25   |

| K.2.3.     | CAUI-4 receiver characteristics                                         | 26   |

| K.2.4.     | Global energy detect function for optional EEE operation                | 28   |

| K.3. CAL   | JI-4 chip-to-chip channel characteristics                               | 328  |

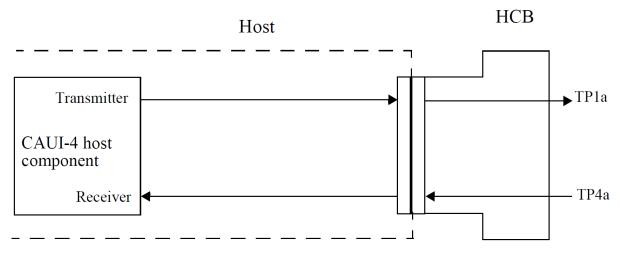

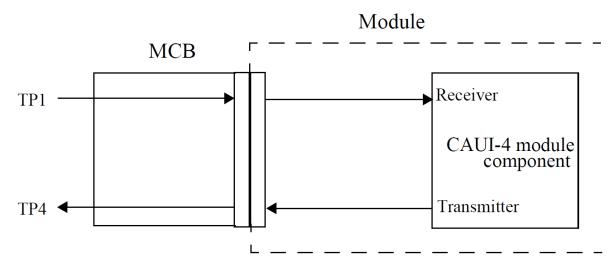

| Annex L | Chip-to-module 100Gb/s four-lane Attachment Unit Interface (CAU 330 | I-4) |

|---------|---------------------------------------------------------------------|------|

| L.1. C  | AUI-4 chip-to-module compliance point definitions                   | 332  |

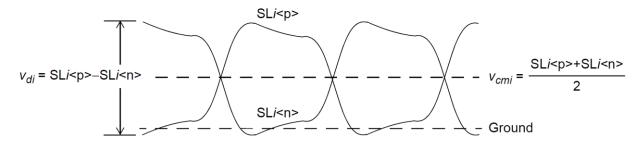

| L.2. (  | CAUI-4 chip-to-module electrical characteristics                    | 333  |

| L.2.    | 1. CAUI-4 host output characteristics                               | 333  |

| L.2.    | 2. CAUI-4 module output characteristics                             | 340  |

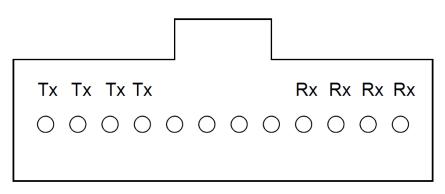

| Annex N | I. Parallel Physical Interface (nPPI) for 100GBASE-SR10 (CPPI)      | 342  |

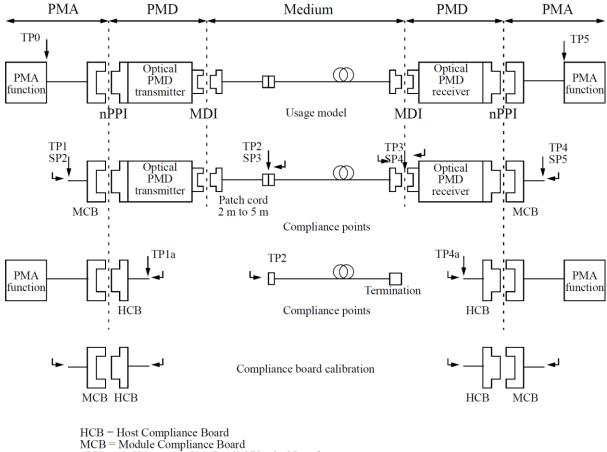

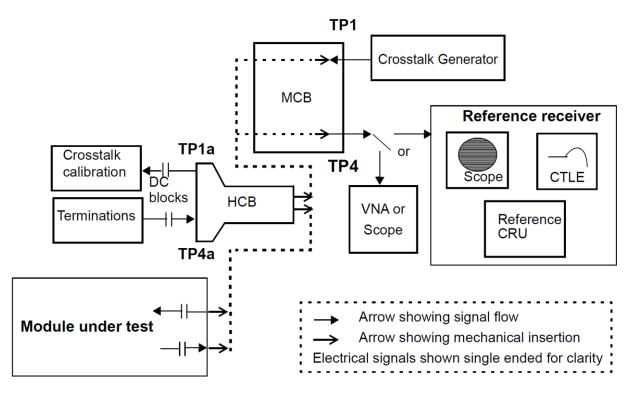

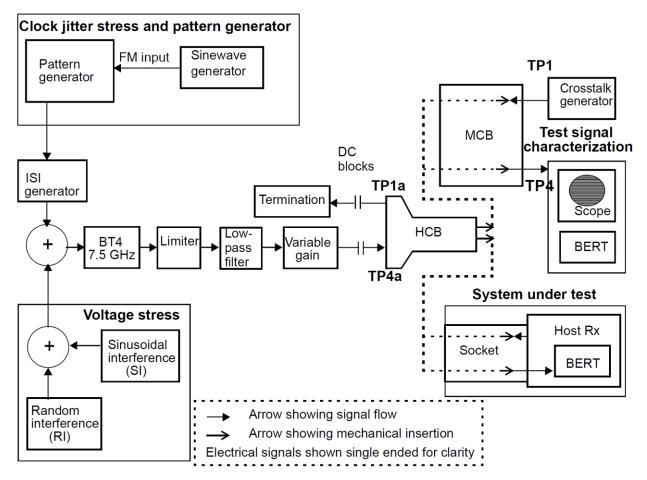

| M.1. E  | Block diagram and test points                                       | 342  |

| M.2. L  | ane assignments                                                     | 342  |

| M.3. E  | Electrical specifications for nPPI                                  | 343  |

| M.3     | .1. nPPI host to module electrical specifications                   | 344  |

| M.3     | .2. nPPI module to host electrical specifications                   | 346  |

| M.4. E  | Definitions of electrical parameters and measurement methods        | 348  |

| M.4     | .1. Test points and compliance boards                               | 348  |

| M.4     | .2. Test patterns and related subsections                           | 353  |

| M.4     | .3. Parameter definitions                                           | 354  |

| 5 Refe  | erences                                                             | 360  |

## **FIGURES**

| Figure 2-1. Architectural positioning of MAC Control sublayer                  |

|--------------------------------------------------------------------------------|

| Figure 2-2. MAC Control sublayer supports of interlayer service interfaces     |

| Figure 2-3. MAC Control frame format                                           |

| Figure 2-4. Architectural positioning of 100Gb/s Ethernet                      |

| Figure 2-5. 100GBASE-R Skew points for single CAUI-n (40BASE-R is out of the   |

| scope of the study)44                                                          |

| Figure 2-6. 100GBASE-R Skew points for multiple CAUI-n (40BASE-R is out of the |

| scope of the study)45                                                          |

| Figure 2-7. 100GBASE-R Skew points with RS-FEC and CAUI-n                      |

| Figure 2-8. RS and MII relationship to the ISO/IEC OSI reference model and the |

| IEEE 802.3 Ethernet model 48                                                   |

| Figure 2-9. Reconciliation Sublayer (RS) inputs and outputs                    |

| Figure 2-10. 100GBASE-R PCS relationship to the ISO/IEC OSI reference model    |

| and IEEE 802.3 Ethernet model51                                                |

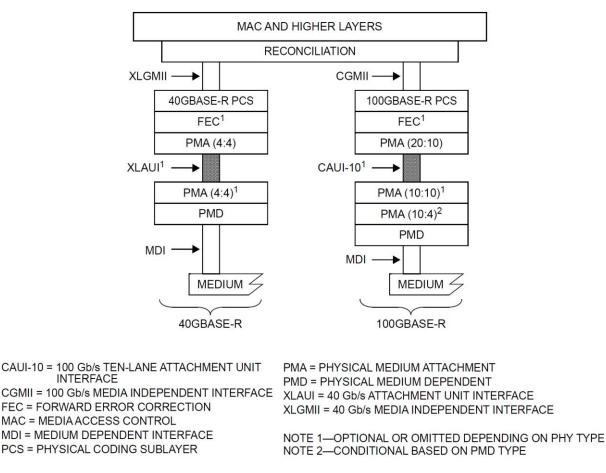

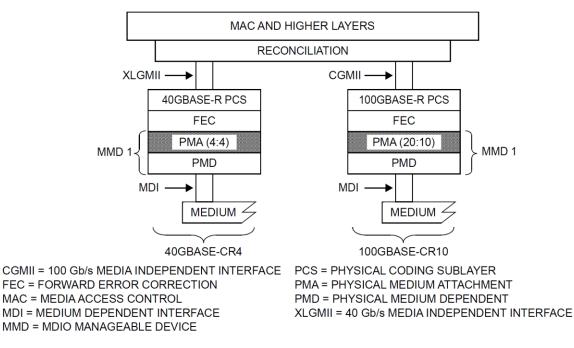

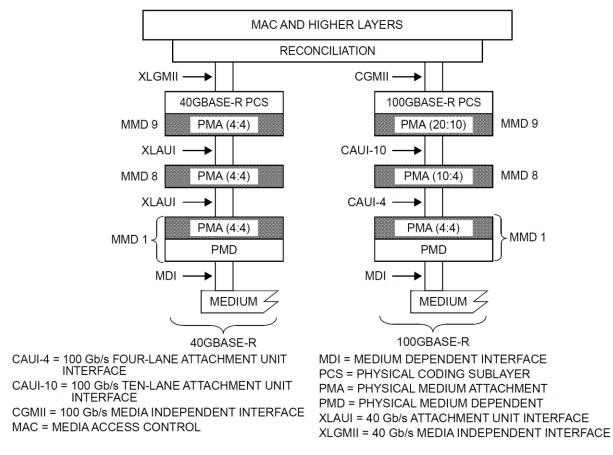

| Figure 2-11. 40GBASE-R and 100GBASE-R PMA relationship to the ISO/IEC OSI      |

| reference model and IEEE 802.3 Ethernet model53                                |

| Figure 2-12. Example 100GBASE-R PMA layering54                                 |

| Figure 2-13. 40GBASE-SR4 and 100GBASE-SR10 PMDs relationship to the            |

| ISO/IEC OSI reference model and IEEE 802.3 Ethernet model                      |

| Figure 2-14. Test points for 100GBASE-SR1060                                   |

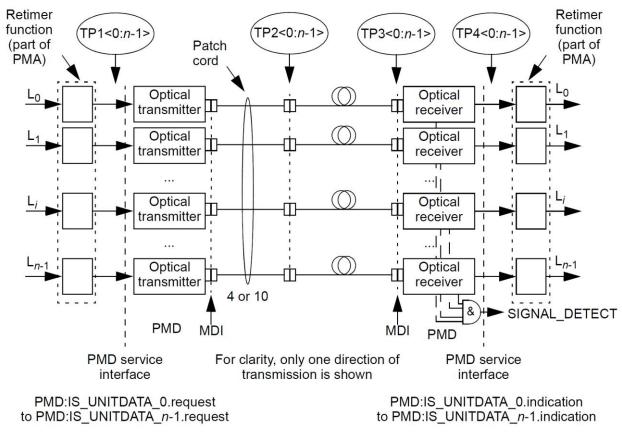

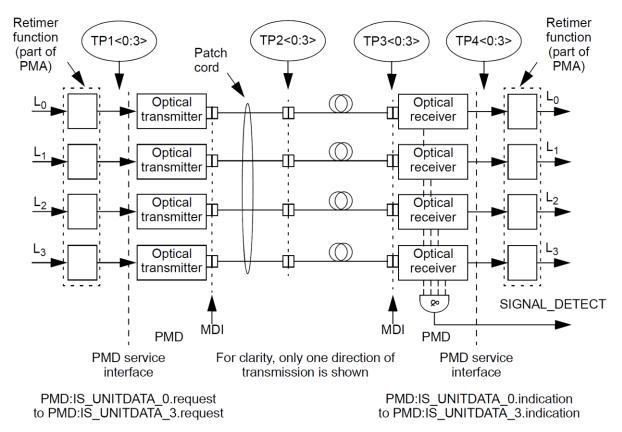

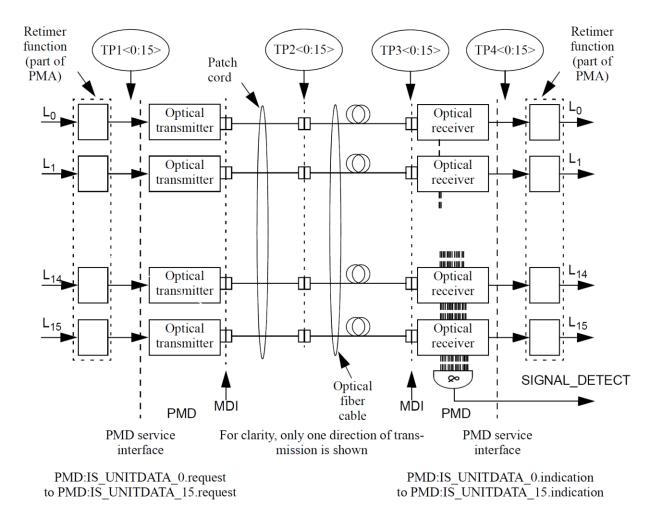

| Figure 2-15. Block diagram for 100GBASE–SR10 transmit/receive paths62          |

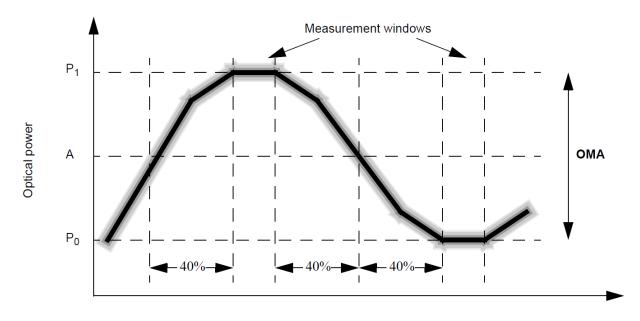

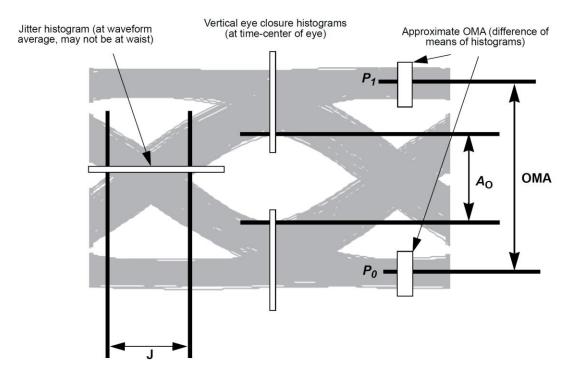

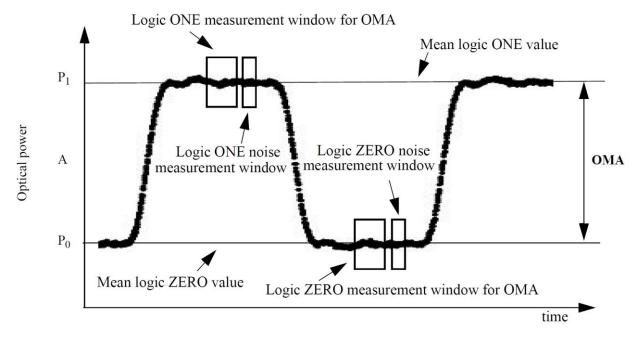

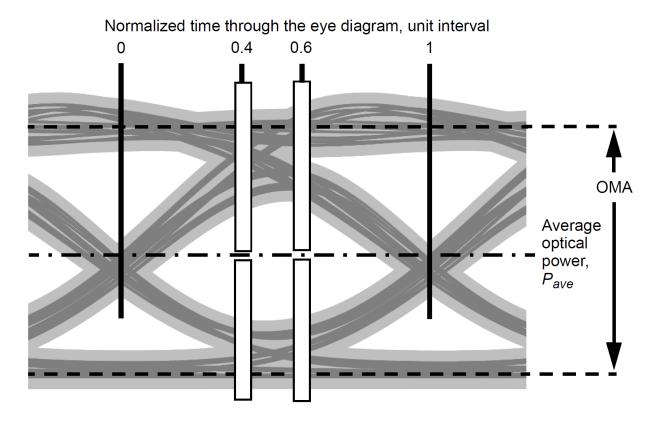

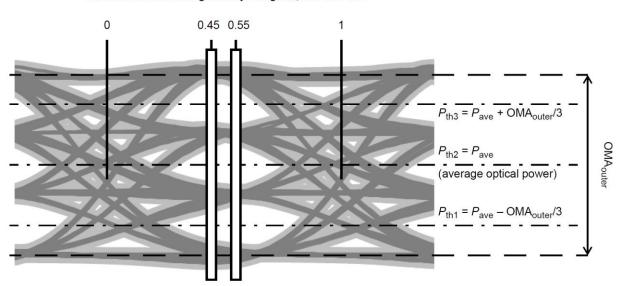

| Figure 2-16. Optical modulation amplitude waveform measurement                 |

| Figure 2-17. Recommended technique for measurement of optical amplitude        |

| modulation72                                                                   |

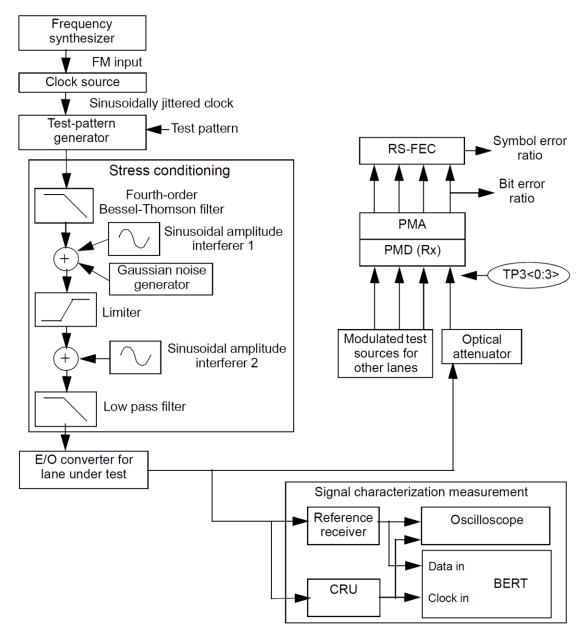

| Figure 2-18. Required characteristics of the test signal at TP3                |

| Figure 2-19. Positions of logic ZERO and logic ONE measurement windows for     |

| OMA and transmitter noise measurements73                                       |

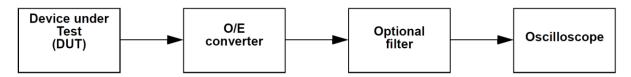

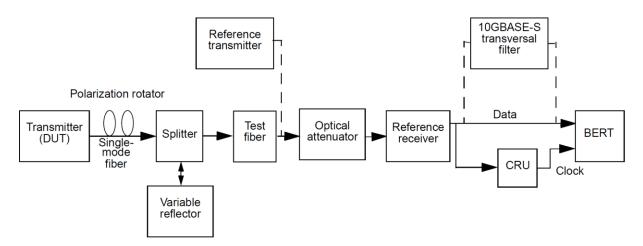

| Figure 2-20. Test setup for the measurement of a transmitter test and for the  |

| dispersion penalty                                                             |

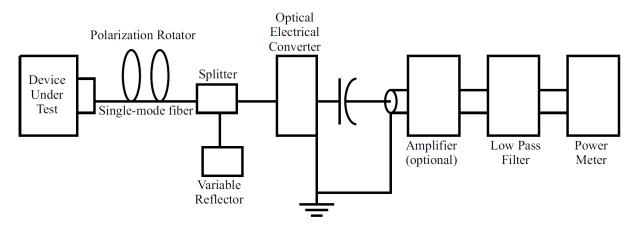

| Figure 2-21. RIN <sub>x</sub> OMA measurement setup75                          |

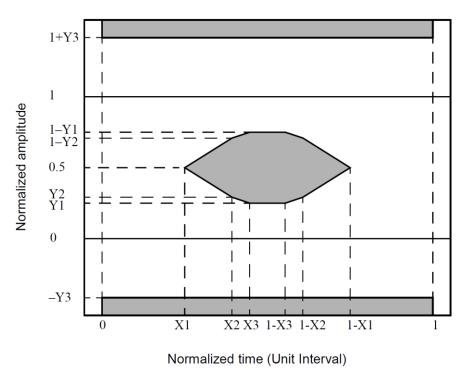

| Figure 2-22. Transmitter eye mask definition                                   |

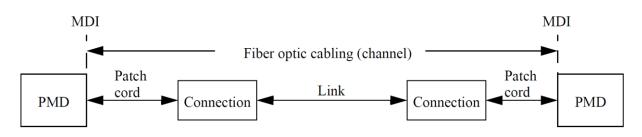

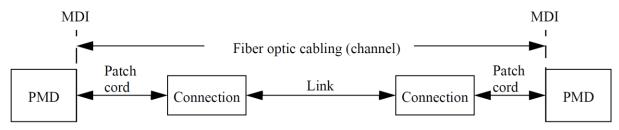

| Figure 2-23. Fiber optic cabling model                                         |

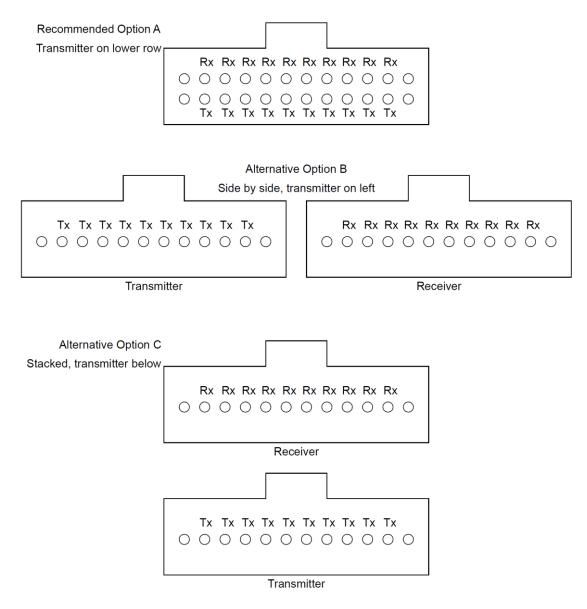

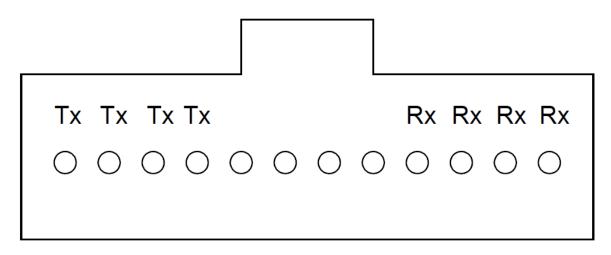

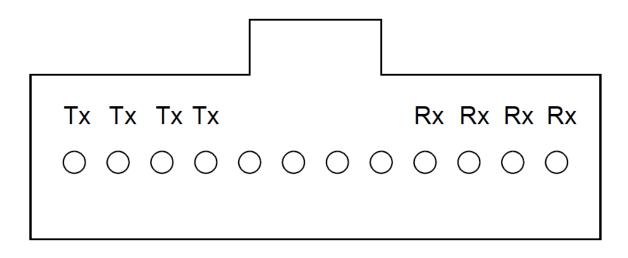

| Figure 2-24. 100GBASE-SR10 optical lane assignments                     |           |

|-------------------------------------------------------------------------|-----------|

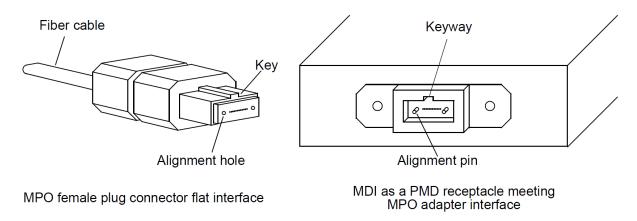

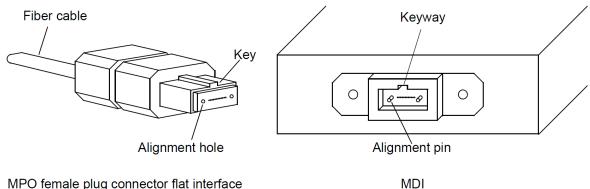

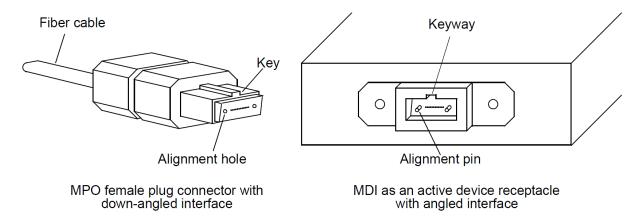

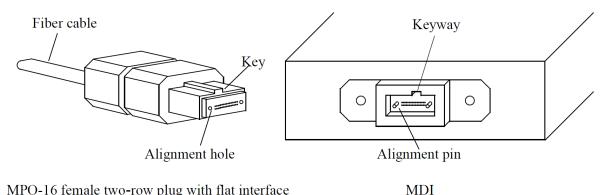

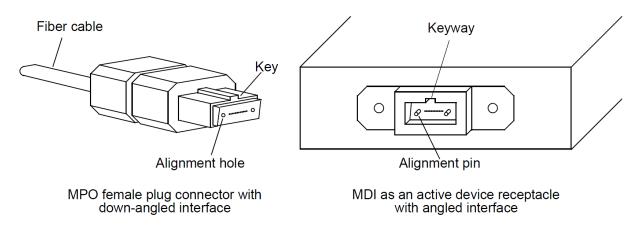

| Figure 2-25. MPO female plug and MDI as a PMD connector using MPC       | adapter.  |

|                                                                         |           |

| Figure 2-26. 100GBASE-LR4 and 100GBASE-ER4 PMDs relationsh              | p to the  |

| ISO/IEC OSI reference model and IEEE 802.3 Ethernet model               |           |

| Figure 2-27. Block diagram for 100GBASE-LR4 and 100GB                   | ASE-ER4   |

| transmit/receive paths                                                  |           |

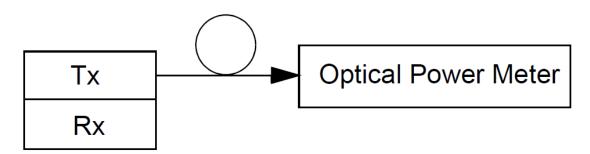

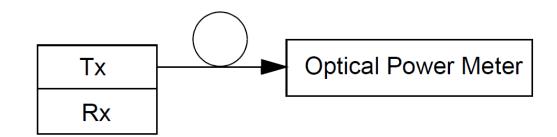

| Figure 2-28. Optical power measurement test set-up.                     | 94        |

| Figure 2-29. Fiber optic cabling model                                  |           |

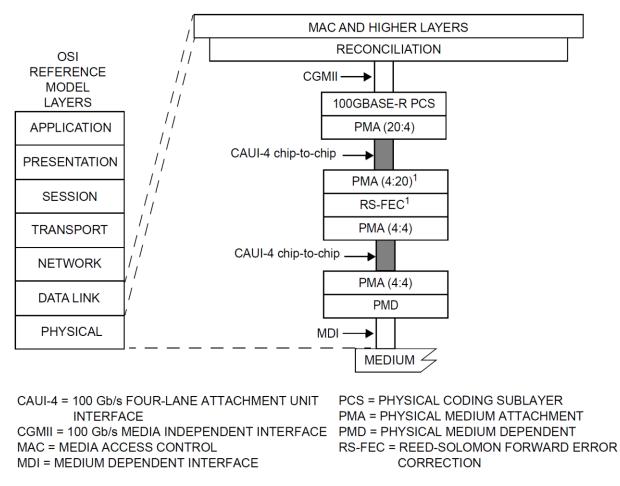

| Figure 2-30. RS-FEC relationship to the ISO/IEC OSI reference model and | the IEEE  |

| 802.3 Ethernet model                                                    | 102       |

| Figure 2-31. Functional block diagram                                   | 105       |

| Figure 2-32. Block lock state diagram                                   | 106       |

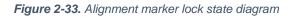

| Figure 2-33. Alignment marker lock state diagram                        | 107       |

| Figure 2-34. PCS deskew state diagram                                   | 108       |

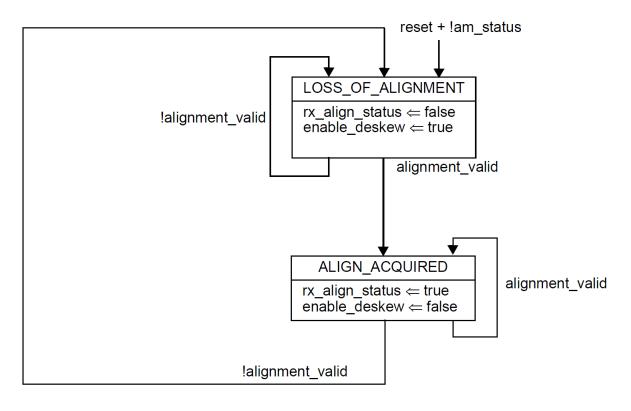

| Figure 2-35. Transmit LPI state diagram                                 | 109       |

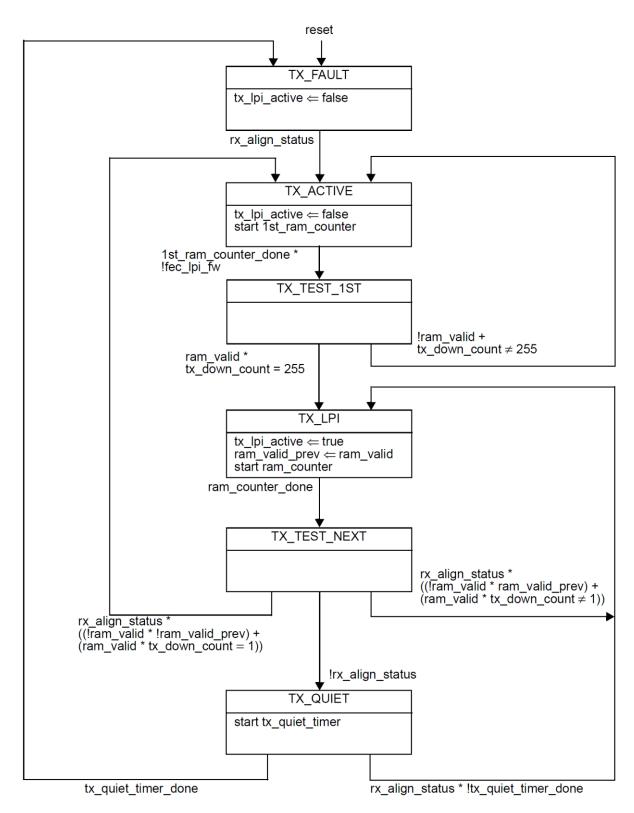

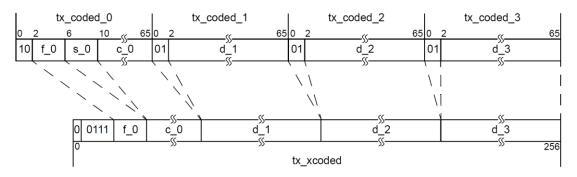

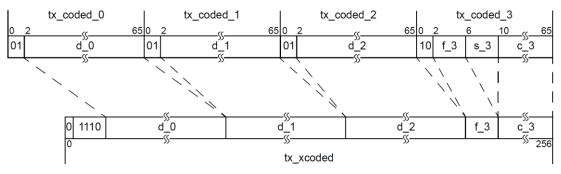

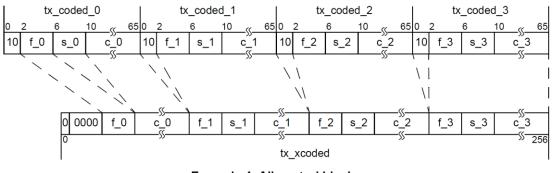

| Figure 2-36. Examples of the construction of tx_xcoded                  | 112       |

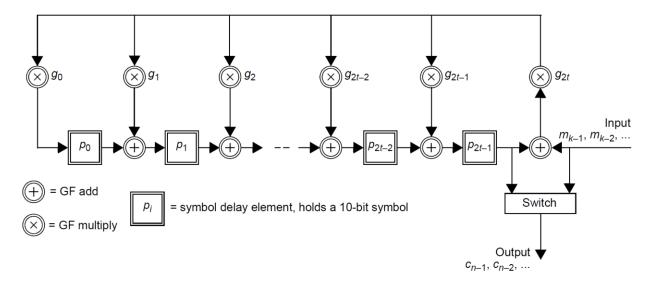

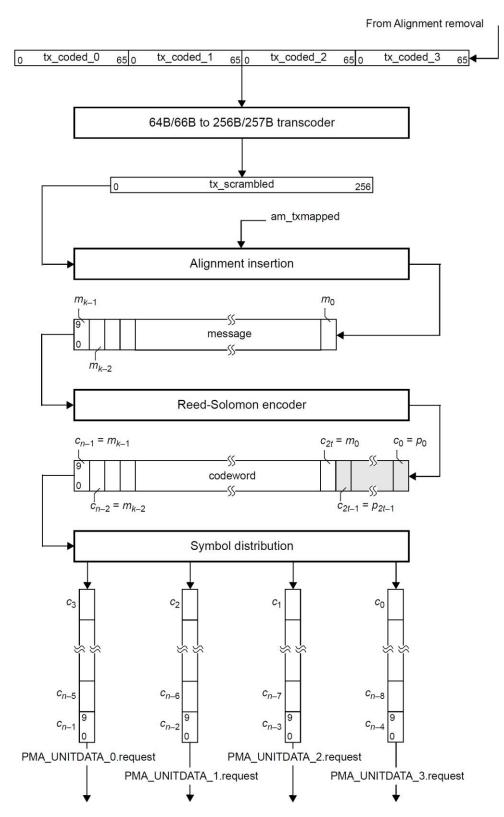

| Figure 2-37. Reed-Solomon encoder functional model                      | 114       |

| Figure 2-38. Transmit bit ordering                                      | 115       |

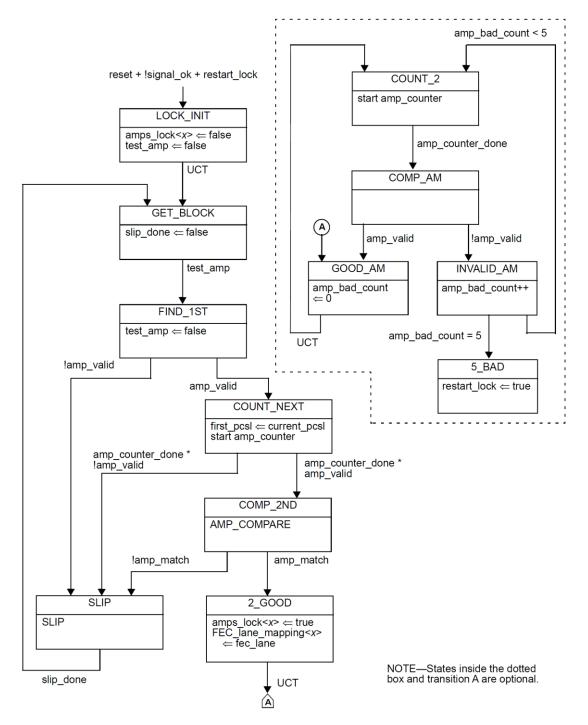

| Figure 2-39. FEC synchronization state diagram.                         | 116       |

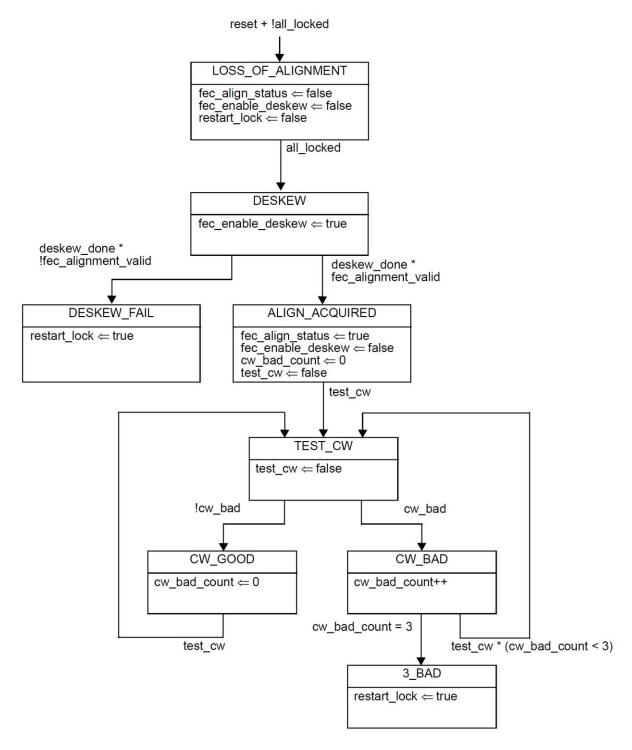

| Figure 2-40. FEC alignment state diagram.                               | 117       |

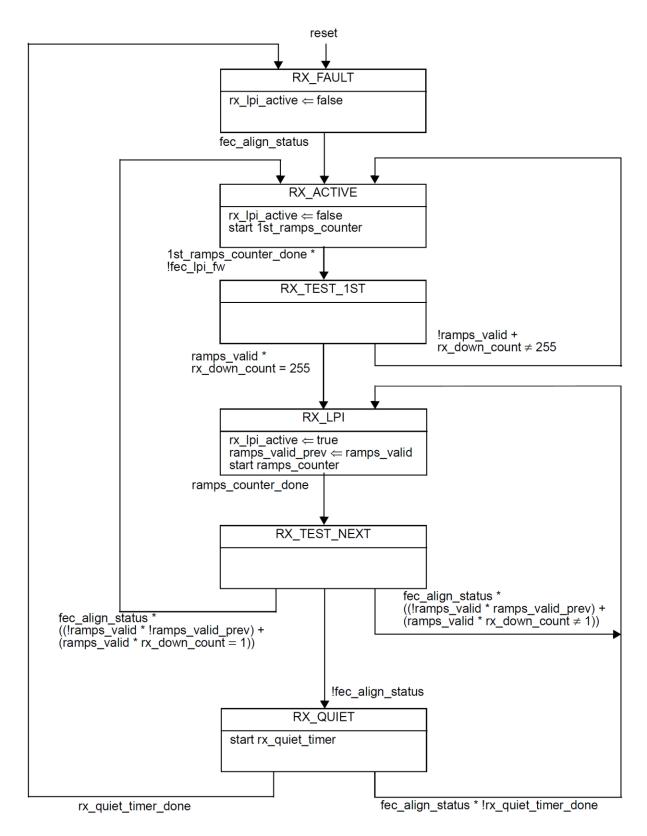

| Figure 2-41. Receive LPI state diagram                                  | 120       |

| Figure 2-42. 64B/66B block formats                                      | 122       |

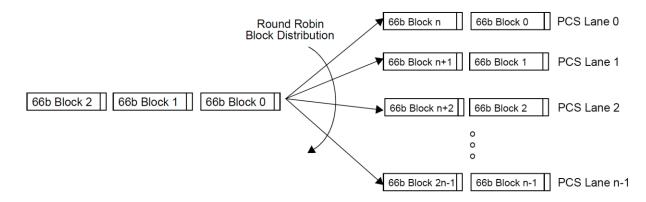

| Figure 2-43. PCS Block distribution.                                    | 123       |

| Figure 2-44. 100GBASE-SR4 PMD relationship of the ISO/IEC OSI           | reference |

| model with the IEEE 802.3 Ethernet model                                | 124       |

| Figure 2-45. Block diagram for 100GBASE-SR4 transmit/receive paths      | 127       |

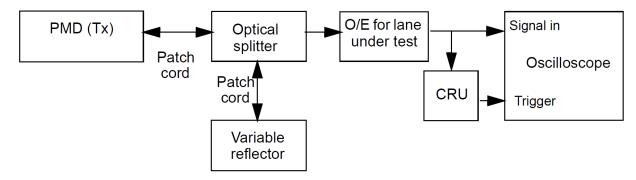

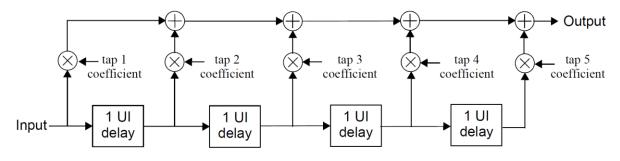

| Figure 2-46. TDEC conformance test block diagram.                       | 134       |

| Figure 2-47. Illustration of the TDEC measurement                       | 135       |

| Figure 2-48. Stressed receiver conformance test block diagram           | 139       |

| Figure 2-49. Fiber optic cabling model                                  | 144       |

| Figure 2-50. 100GBASE-SR4 optical lane assignments.                     | 146       |

| Figure 2-51. MPO female plug with flat interface and MDI                | 146       |

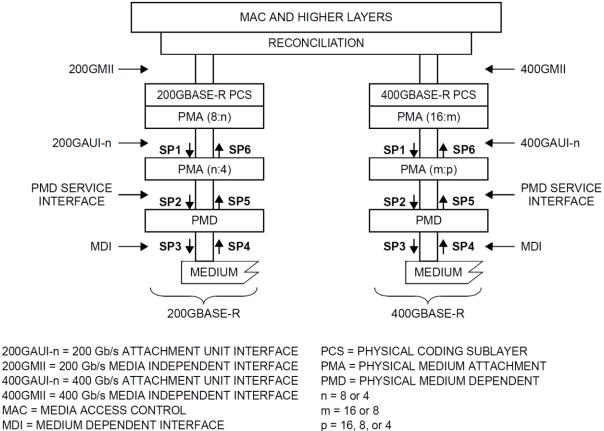

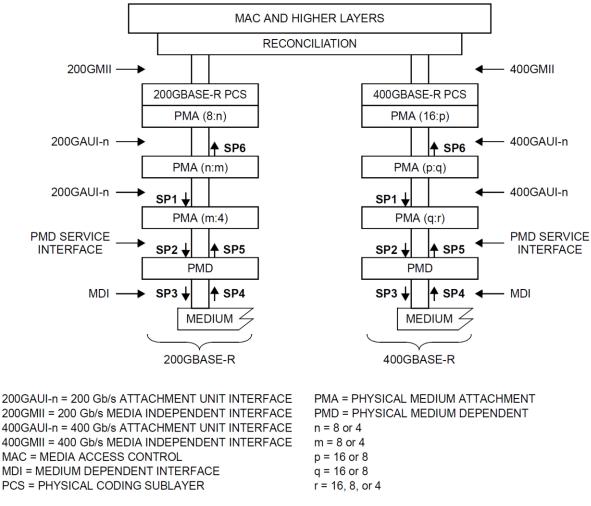

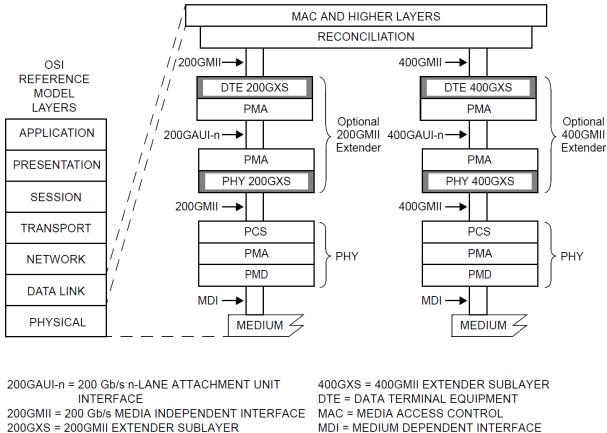

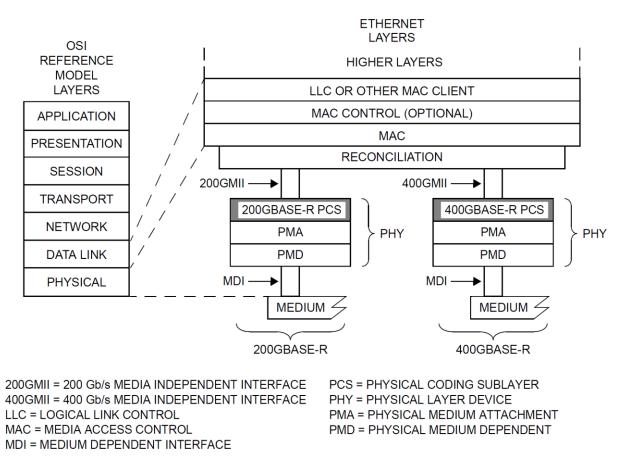

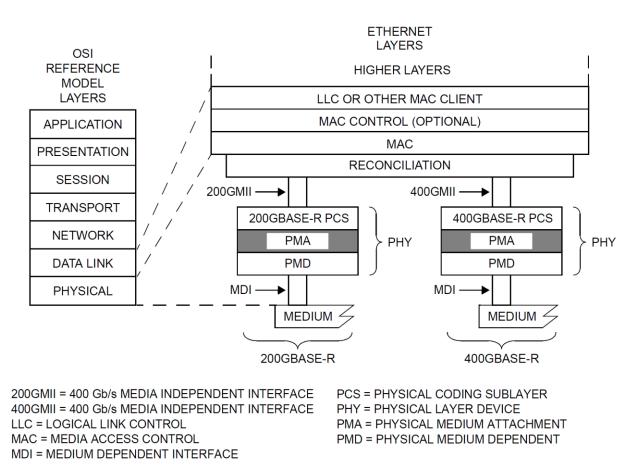

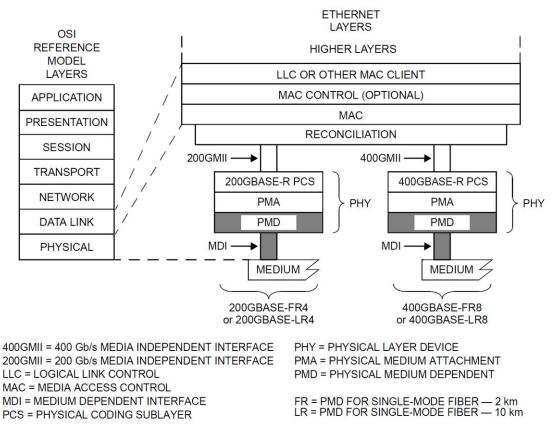

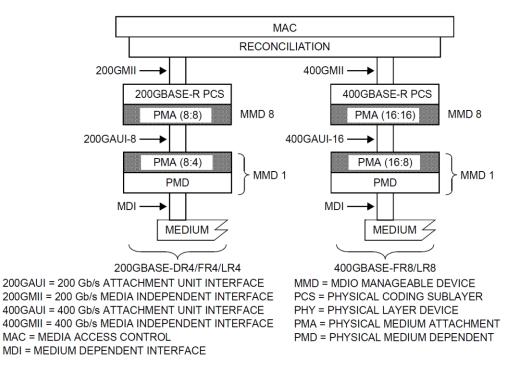

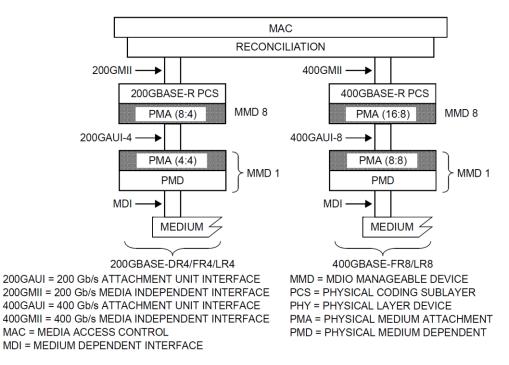

| Figure 3-1. Architecture of 200Gb/s and 400Gb/s Ethernet                        |

|---------------------------------------------------------------------------------|

| Figure 3-2. MAC control sublayer150                                             |

| Figure 3-3. MAC services150                                                     |

| Figure 3-4. MAC packet format151                                                |

| Figure 3-5. 200GBASE-R and 400GBASE-R Skew points for single 200GAUI-n or       |

| 400GAUI-n                                                                       |

| Figure 3-6. 200GBASE-R and 400GBASE-R Skew points for multiple 200GAUI-n        |

| or 400GAUI-n                                                                    |

| Figure 3-7. RS and MII in IEEE 802.3 Ethernet model                             |

| Figure 3-8. 200GXS and 400GXS in IEEE 802.3 Ethernet model                      |

| Figure 3-9. Remote Degrade signaling without XS                                 |

| Figure 3-10. Local Degrade signaling with XS162                                 |

| Figure 3-11. Remote Degrade signaling with XS                                   |

| Figure 3-12. 200GBASE-R and 400GBASE-R PCS                                      |

| Figure 3-13. 200GBASE-R and 400GBASE-R PMA166                                   |

| Figure 3-14. Example 200GBASE-R and 400GBASE-R PMA layering167                  |

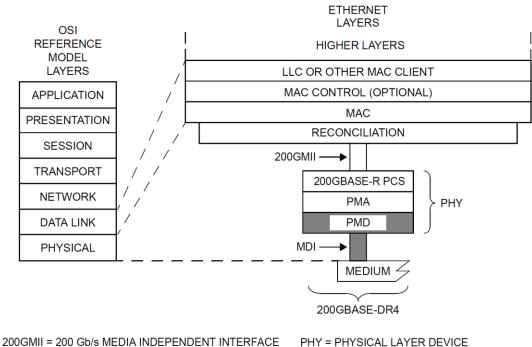

| Figure 3-15. 200GBASE-DR4 PMD                                                   |

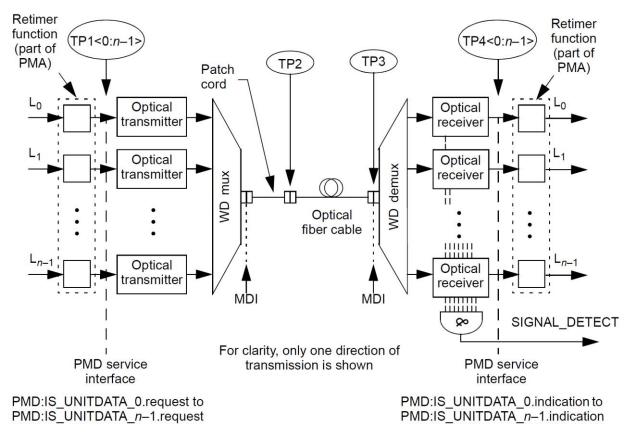

| Figure 3-16. Block diagram for 200GBASE-DR4 transmit/receive paths              |

| Figure 3-17. Optical power measurement test set-up                              |

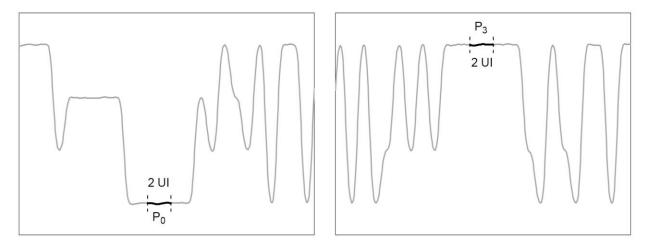

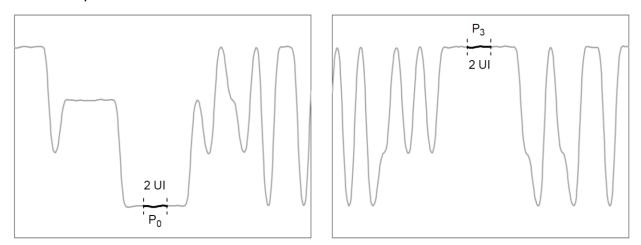

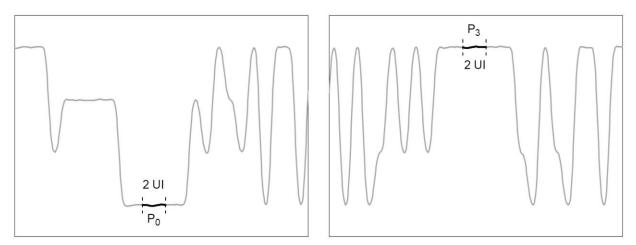

| Figure 3-18. Example power levels $P_0$ and $P_3$ from PRBS13Q test pattern 178 |

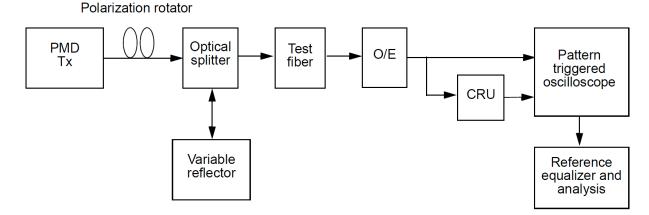

| Figure 3-19. TDECQ conformance test block diagram                               |

| Figure 3-20. Illustration of the TDECQ measurement                              |

| Figure 3-21. TDECQ reference equalizer functional model                         |

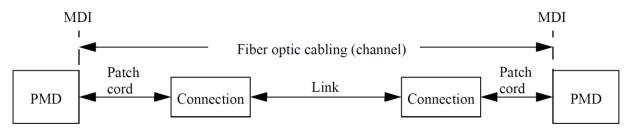

| Figure 3-22. Fiber optic cabling model184                                       |

| Figure 3-23. 200GBASE-DR4 optical lane assignments                              |

| Figure 3-24. MPO female plug with down-angled interface and MDI active device   |

| connector with angled interface                                                 |

| Figure 3-25. 200GBASE-FR4, 200GBASE-LR4, 400GBASE-FR8, and 400GBASE-            |

| LR8 PMDs                                                                        |

| Figure 3-26. Block diagram for 200GBASE-FR4, 200GBASE-LR4, 400GBASE-            |

| FR8, and 400GBASE-LR8 transmit/receive paths                                    |

| Figure 3-27. Power levels $P_0$ and $P_3$ from PRBS13Q test pattern             |

| Figure 3-28. TDECQ conformance test block diagram                               |

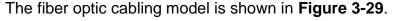

| Figure 3-29. Fiber optic cabling model                                          |

|---------------------------------------------------------------------------------|

| Figure 3-30. 400GBASE-SR16 PMD                                                  |

| Figure 3-31. Block diagram for 400GBASE-SR16 transmit/receive paths213          |

| Figure 3-32. Fiber optic cabling model218                                       |

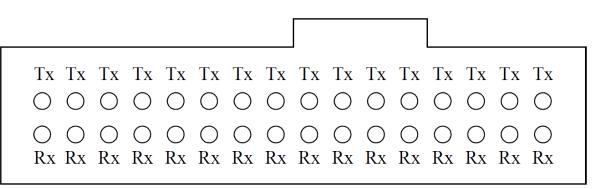

| Figure 3-33. 400GBASE-SR16 optical lane assignments                             |

| Figure 3-34. MPO-16 female two-row plug with flat interface, and an MDI 221     |

| Figure 3-35. 400GBASE-DR4 PMD                                                   |

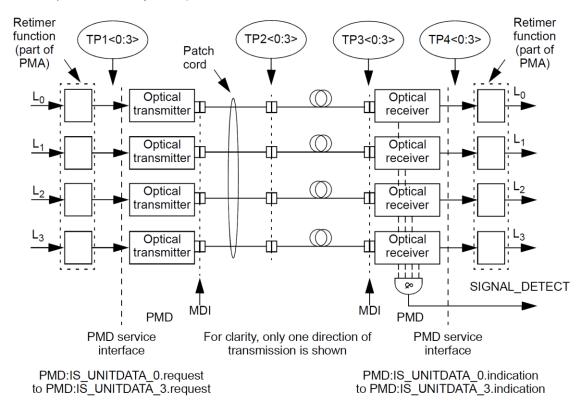

| Figure 3-36. Block diagram for 400GBASE-DR4 transmit/receive paths              |

| Figure 3-37. Example power levels $P_0$ and $P_3$ from PRBS13Q test pattern 230 |

| Figure 3-38. Fiber optic cabling model                                          |

| Figure 3-39. 400GBASE-DR4 optical lane assignments                              |

| Figure 3-40. MPO female plug with down-angled interface and MDI active device   |

| connector with angled interface236                                              |

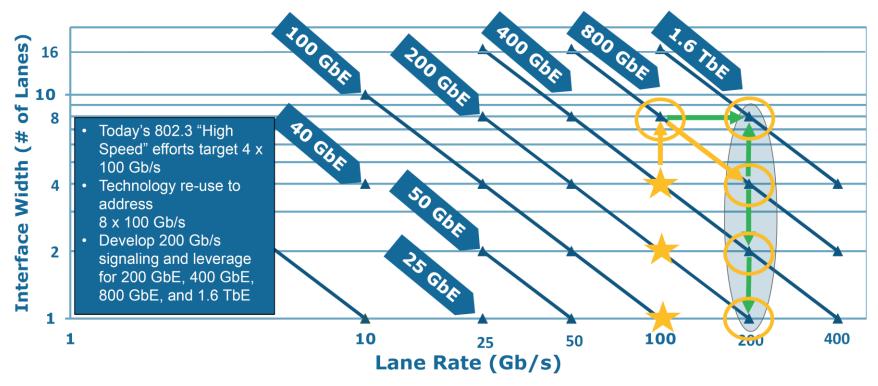

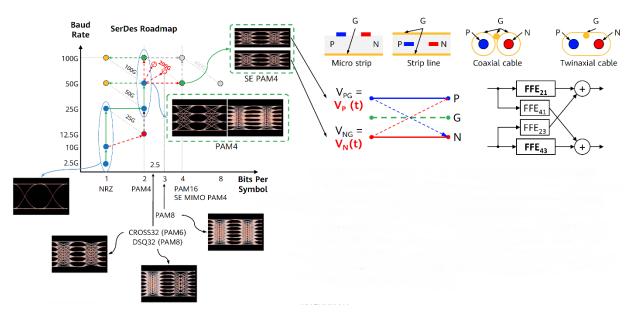

| Figure 4-1. Leveraged Signaling Technologies Across Ethernet Rates              |

| Figure 4-2. Adopted Physical Layer Objectives and technology reuse              |

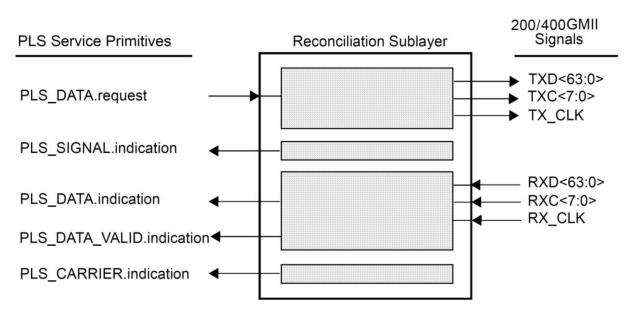

| Figure 4-3. Reconciliation sublayer for 200 and 400Gb/s Ethernet                |

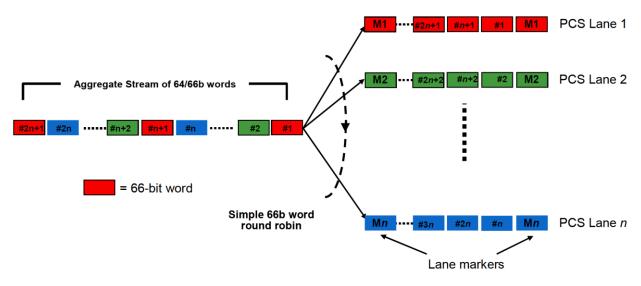

| Figure 4-4. PCS Multilane Distribution Concept248                               |

| Figure 4-5. Current 100Gb/s per lane AUI generation                             |

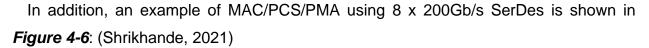

| Figure 4-6. Future 200G/lane AUI generation249                                  |

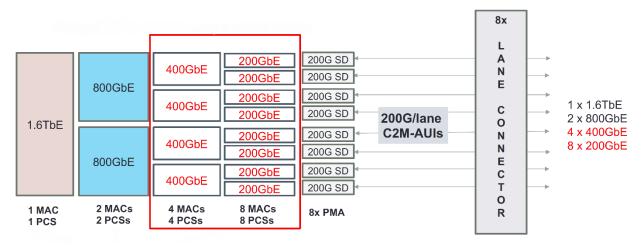

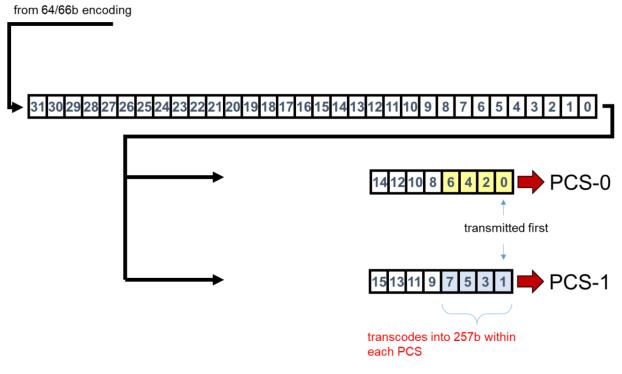

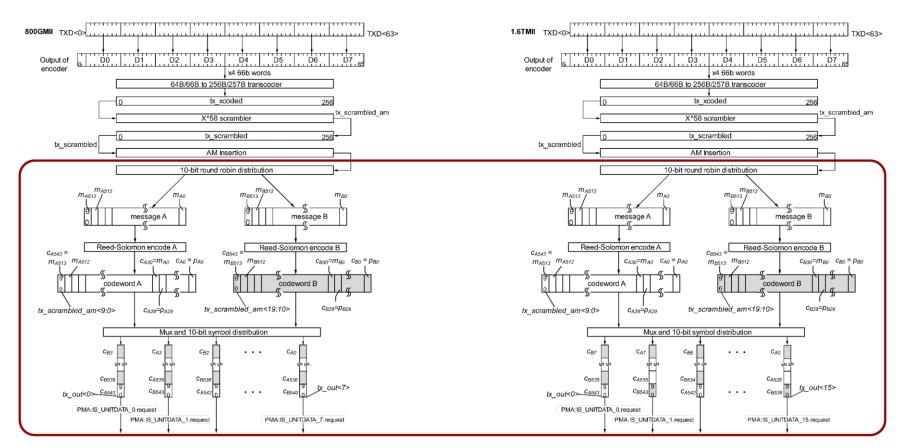

| Figure 4-7. 800Gb/s PCS transmit flow250                                        |

| Figure 4-8. 66B block Round Robin distribution251                               |

| Figure 4-9. 800Gb/s PCS receive flow252                                         |

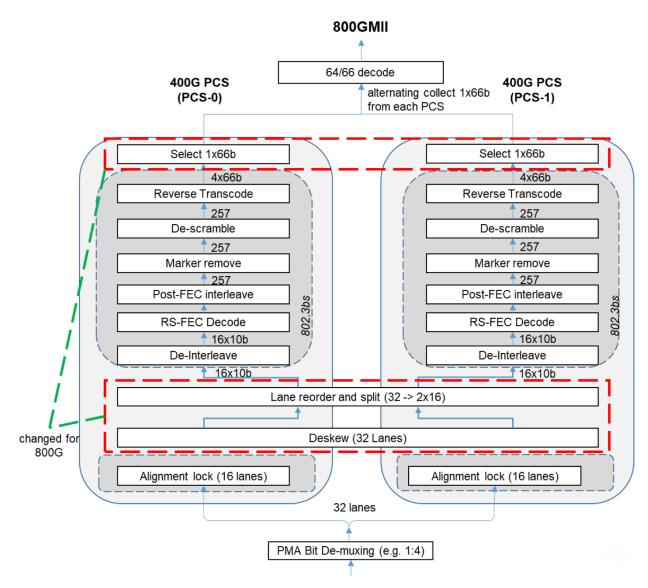

| Figure 4-10. 400 Gb/s PCSs253                                                   |

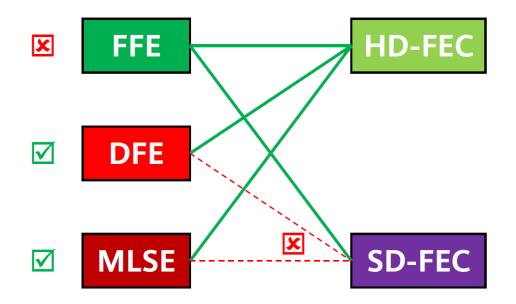

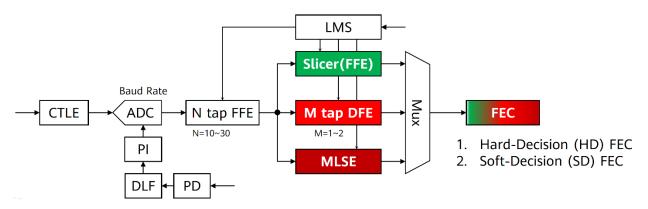

| Figure 4-11. FEC Schemes for 800Gb/s and 1.6Tb/s Ethernet rates                 |

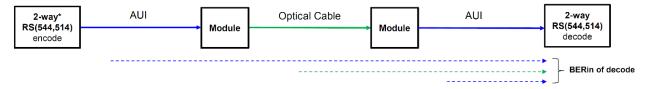

| Figure 4-12. End-to-End FEC Scheme                                              |

| Figure 4-13. FEC Sublayer Allocation for End-to-End FEC Scheme                  |

| Figure 4-14. Concatenated FEC Code256                                           |

| Figure 4-15. Encapsulated or Concatenated FEC Scheme                            |

| Figure 4-16. FEC Sublayer Allocation for Encapsulated or Concatenated FEC       |

| Scheme                                                                          |

| Figure 4-17. Proposed FEC1 Code                                                 |

| Figure 4-18. Segmented FEC Scheme                                               |

| Figure 4-19. FEC Sublayer Allocation for Segmented FEC Scheme                   |

| Figure 4-20. Relationship of FEC and DSP                 | . 264 |

|----------------------------------------------------------|-------|

| Figure 4-21. New Approach of DSP Architecture            | . 265 |

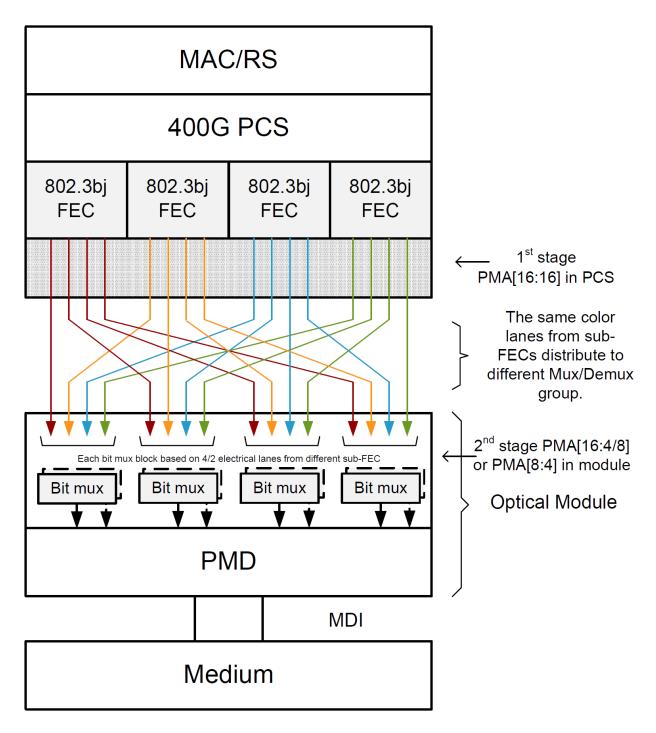

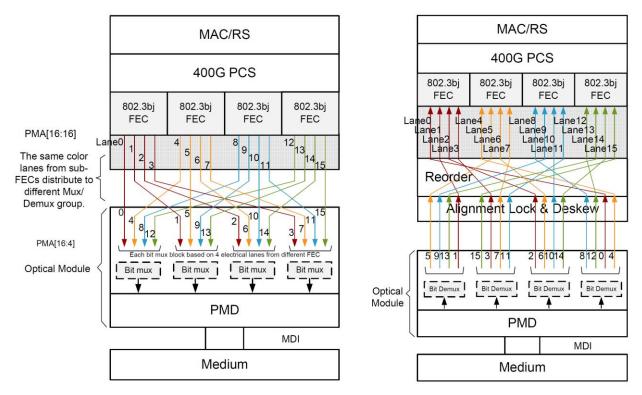

| Figure 4-22. Improved PCS/PMA architecture with bit-mux  | . 267 |

| Figure 4-23. FEC lanes alignment and reorder mechanism   | . 268 |

| Figure 4-24. Beyond 100Gb/s SerDes (PMA)                 | . 269 |

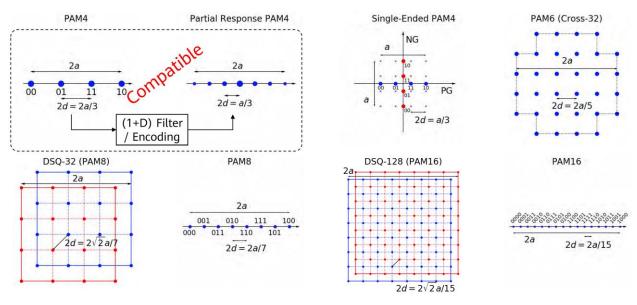

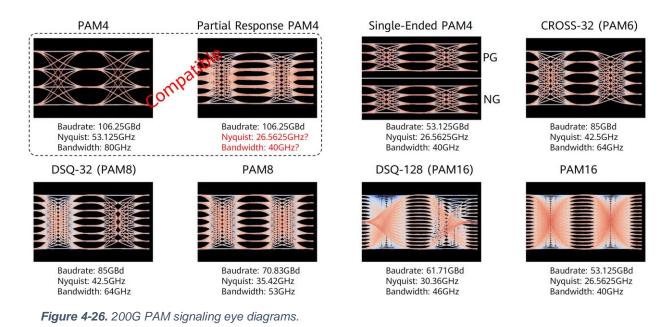

| Figure 4-25. 200G PAM signaling constellations           | . 269 |

| Figure 4-26. 200G PAM signaling eye diagrams             | . 270 |

| Figure 4-27. Comparison of 200Gb/s PAM signaling schemes | . 270 |

# **TABLES**

| Table 2-1. 100Gb/s PHYs                                                          | 41     |

|----------------------------------------------------------------------------------|--------|

| Table 2-2.         Sublayer delay constraints.                                   | 42     |

| Table 2-3.         Summary of Skew constraints.                                  | 43     |

| Table 2-4.         Summary of Skew Variation constraints.                        | 46     |

| Table 2-5.         Delay constraints.                                            | 49     |

| Table 2-6.         MDIO Manageable Device addresses.                             | 55     |

| Table 2-7. Physical Layer Sections associated with the 100GBASE-SR10 P           | MDs.   |

|                                                                                  | 57     |

| Table 2-8.         Summary of 100GBASE–SR10.                                     | 58     |

| Table 2-9.         SIGNAL_DETECT value definition.                               | 63     |

| Table 2-10. Optical fiber and cable characteristics.                             | 65     |

| Table 2-11.         100GBASE-SR10 optical transmit characteristics.              | 65     |

| Table 2-12. Characteristics of signal within, and at the receiving end of, a com | pliant |

| optical channel                                                                  | 66     |

| Table 2-13.         100GBASE-SR10 optical receiver characteristics.              | 67     |

| Table 2-14. 40GBASE-SR4 or 100GBASE-SR10 illustrative link power buc             | dgets. |

|                                                                                  | 67     |

| Table 2-15.         Parameters defined at each test point.                       | 68     |

| Table 2-16. Test patterns                                                        | 69     |

| Table 2-17.         Test patterns and related subsections.                       | 69     |

| Table 2-18. Test patterns                                                        | 71     |

| Table 2-19.         Pattern segments.                                            | 72     |

| Table 2-20.         Fiber optic cabling (channel) characteristics at 850nm       | 80     |

| Table 2-21. Optical fiber and cable characteristics.                             | 81     |

| Table 2-22. PHY sections associated with the 100GBASE-LR4 and 100GB              | ASE-   |

| ER4 PMDs                                                                         | 84     |

| Table 2-23.         SIGNAL_DETECT value definition.                              | 89     |

| Table 2-24.         Wavelength-division-multiplexed lane assignments.            | 89     |

| Table 2-25. 100GBASE-LR4 and 100GBASE-ER4 operating ranges                       | 90     |

| Table 2-26. 100GBASE-LR4 and 100GBASE-ER4 transmit characteristics               | 91     |

| Table 2-27. 100GBASE-LR4 and 100GBASE-ER4 receive characteristics                | 92     |

| Table 2-28. 100GBASE-LR4 and 100GBASE-ER4 illustrative link power budge      | ets. |

|------------------------------------------------------------------------------|------|

|                                                                              | 93   |

| Table 2-29.         Test-pattern definitions and related sections.           | 94   |

| Table 2-30.    Test patterns.                                                | 94   |

| Table 2-31.         Transmitter compliance channel specifications.           | 96   |

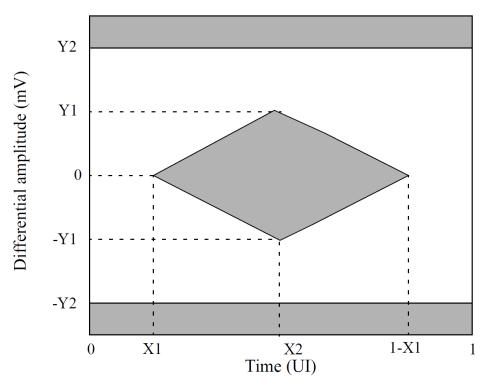

| Table 2-32. Applied sinusoidal jitter.                                       | 98   |

| Table 2-33. Fiber optic cabling (channel) characteristics                    | 00   |

| Table 2-34. Optical fiber and cable characteristics.         1               | 00   |

| Table 2-35. Coefficients of the generator polynomial gi (decimal).         1 | 14   |

| Table 2-36. PHY sections associated with the 100GBASE-SR4 PMD.         1     | 24   |

| Table 2-37. SIGNAL_DETECT value definition.         1                        | 28   |

| Table 2-38.         100GBASE-SR4 operating range                             | 29   |

| Table 2-39.         100GBASE-SR4 transmit characteristics.         1         | 130  |

| Table 2-40.         100GBASE-SR4         receive characteristics             | 31   |

| Table 2-41.         100GBASE-SR4 illustrative link power budget.         1   | 31   |

| Table 2-42.         Test-pattern definitions and related sections.         1 | 32   |

| Table 2-43. Test patterns.         1                                         | 32   |

| Table 2-44. Applied sinusoidal jitter1                                       | 43   |

| Table 2-45. Fiber optic cabling (channel) characteristics for 100GBASE-SR41  | 44   |

| Table 2-46. Optical fiber and cable characteristics.         1               | 45   |

| <b>Table 3-1.</b> 200Gb/s PHYs 1                                             | 49   |

| <b>Table 3-2.</b> 400Gb/s PHYs 1                                             | 49   |

| Table 3-3.         Sublayer delay constraints (200GBASE)                     | 52   |

| Table 3-4.         Sublayer delay constraints (400GBASE)                     | 53   |

| Table 3-5.         Summary of Skew constraints.         1                    | 56   |

| Table 3-6.         Summary of Skew Variation constraints.         1          | 56   |

| Table 3-7. MDIO Manageable Device addresses.         1                       | 68   |

| Table 3-8. PHY paragraphs associated with the 200GBASE-DR4 PMD 1             | 170  |

| Table 3-9.         SIGNAL_DETECT value definition.         1                 | 173  |

| Table 3-10.         200GBASE-DR4 operating range         1                   | 174  |

| Table 3-11.         200GBASE-DR4 transmit characteristics.         1         | 175  |

| Table 3-12.         200GBASE-DR4         receive characteristics.         1  | 176  |

| Table 3-13.         200GBASE-DR4 illustrative link power budget         1    | 176  |

| Table 3-14.    Test patterns.    177                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------|

| Table 3-15. Test-pattern definitions and related sections.         177                                                   |

| Table 3-16.         Transmitter compliance channel specifications.         180                                           |

| Table 3-17. Fiber optic cabling (channel) characteristics                                                                |

| Table 3-18. Optical fiber and cable characteristics.         185                                                         |

| Table 3-19. Maximum value of each discrete reflectance                                                                   |

| Table 3-20. Physical Layer sections associated with the 200GBASE-FR4,                                                    |

| 200GBASE-LR4, 400GBASE-FR8, and 400GBASE-LR8 PMDs                                                                        |

| Table 3-21. SIGNAL_DETECT value definition.         192                                                                  |

| Table 3-22.         200GBASE-FR4         wavelength-division-multiplexed         lane         assignments.           193 |

| Table 3-23.         200GBASE-LR4         wavelength-division-multiplexed         lane         assignments.               |

|                                                                                                                          |

| Table 3-24. 400GBASE-FR8 and 400GBASE-LR8 wavelength-division-multiplexed                                                |

| lane assignments                                                                                                         |

| Table 3-25. 200GBASE-FR4, 200GBASE-LR4, 400GBASE-FR8, and 400GBASE-                                                      |

| LR8 operating ranges                                                                                                     |

| Table 3-26. 200GBASE-FR4 and 200GBASE-LR4 transmit characteristics 196                                                   |

| Table 3-27. 400GBASE-FR8 and 400GBASE-LR8 transmit characteristics 197                                                   |

| Table 3-28. 200GBASE-FR4 and 200GBASE-LR4 receive characteristics 198                                                    |

| Table 3-29. 400GBASE-FR8 and 400GBASE-LR8 receive characteristics 199                                                    |

| Table 3-30. 200GBASE-FR4, 200GBASE-LR4, 400GBASE-FR8, and 400GBASE-                                                      |

| LR8 illustrative link power budgets                                                                                      |

| Table 3-31. Test patterns.    201                                                                                        |

| Table 3-32.         Test-pattern definitions and related sections.         201                                           |

| Table 3-33.         Transmitter compliance channel specifications.         204                                           |

| Table 3-34. Fiber optic cabling (channel) characteristics                                                                |

| Table 3-35. Optical fiber and cable characteristics.         209                                                         |

| Table 3-36. Maximum value of each discrete reflectance                                                                   |

| Table 3-37. Physical Layer sections associated with the 400GBASE-SR16 PMD.                                               |

|                                                                                                                          |

| Table 3-38. SIGNAL_DETECT value definition.         214                                                                  |

| Table 3-39.         400GBASE-SR16 operating range                                                                        |

| Table 3-40. Fiber optic cabling (channel) characteristics for 400GBASE-SR16. 219         |

|------------------------------------------------------------------------------------------|

| Table 3-41. Optical fiber and cable characteristics.         220                         |

| Table 3-42. Physical Layer sections associated with the 400GBASE-DR4 PMD                 |

|                                                                                          |

| Table 3-43. SIGNAL_DETECT value definition.         225                                  |

| Table 3-44.         400GBASE-DR4 operating range                                         |

| Table 3-45.         400GBASE-DR4 transmit characteristics.         227                   |

| Table 3-46. 400GBASE-DR4 receive characteristics.         228                            |

| Table 3-47.         400GBASE-DR4 illustrative link power budget                          |

| Table 3-48. Test patterns.    229                                                        |

| Table 3-49. Test-pattern definitions and related sections.         229                   |

| Table 3-50. Fiber optic cabling (channel) characteristics                                |

| Table 3-51. Optical fiber and cable characteristics.         234                         |

| Table 3-52. Maximum value of each discrete reflectance                                   |

| Table 4-1. Adopted physical layer objectives landscape.         242                      |

| Table 4-2.         Assumptions of Electrical/Optical Lanes for FEC Analysis.         255 |

| Table 4-3.    Proposed FEC1 Characteristics.    261                                      |

| Table 4-4. FEC approaches to support proposed BER objectives                             |

# **Abbreviations**

| ADC     | Analogue-to-Digital Converter                          |

|---------|--------------------------------------------------------|

| AN      | Auto-Negotiation                                       |

| ANR     | Amplitude-to-Noise Ratio                               |

| ASIC    | Application-Specific Integrated Circuit                |

| BCH     | Bose, Ray-Chaudhuri, and Hocquenghem                   |

| BCJR    | Bahl, Cocke, Jelinek, Raviv                            |

| BER     | Bit Error Ratio                                        |

| BPS     | Blind Phase Search                                     |

| BRE     | Bridge Relay Entity,                                   |

| BT      | Bit Time                                               |

| C2C     | Chip-to-Chip                                           |

| C2M     | Chip-to-Module                                         |

| CAUI-4  | 100Gb/s four-lane Attachment Unit Interface            |

| CAUI-10 | 100Gb/s ten-lane Attachment Unit Interface             |

| CD      | Chromatic Dispersion                                   |

| CFC     | Carrier Frequency Compensation                         |

| CFEC    | Concatenated FEC                                       |

| COM     | Channel Operating Margin                               |

| CPC     | Carrier Phase Compensation                             |

| CPPI    | 100Gb/s Parallel Physical Interface                    |

| CRU     | Clock Recovery Unit                                    |

| CSMA/CD | Carrier Sense Multiple Access with Collision Detection |

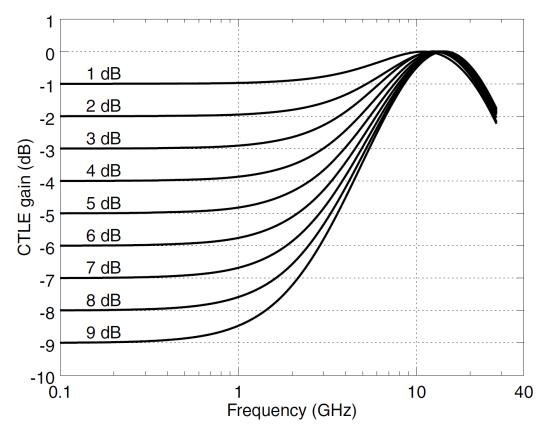

| CTLE    | Continuous Time Linear Equalizer                       |

| DD      | Direct Detect                                          |

| DDJ     | Data Depend Jitter                                     |

| DDPWS   | Data Dependent Pulse Width Shrinkage                   |

| DFE     | Decision Feedback Equalizer                            |

| DGD     | Differential Group Delay                               |

| DIC     | Deficit Idle Counter                                   |

| DLF     | Delay Line Filter                                      |

| DLL     | Data Link Layer                                        |

| DSP     | Digital Signal Processor                               |

|         |                                                        |

| DTE    | Data Terminal Equipment                    |

|--------|--------------------------------------------|

| DUT    | Device Under Test                          |

| DWDM   | Dense Wavelength Division Multiplexing     |

| EEE    | Energy Efficient Ethernet                  |

| EQ     | EQualization                               |

| FCS    | Frame Check Sequence                       |

| FEC    | Forward Error Correction                   |

| FFE    | Feed-Forward Equalizer                     |

| CGMII  | 100Gb/s Media Independent Interface        |

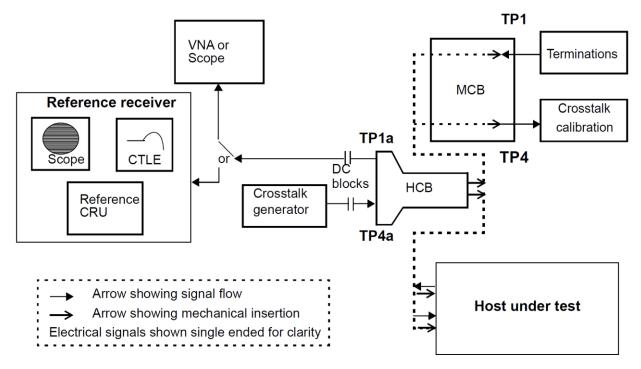

| HCB    | Host Compliance Board                      |

| HD-FEC | Hard-Decision FEC                          |

| IEC    | International Electrotechnical Committee   |

| IL     | Insertion Loss                             |

| ILD    | Insertion Loss Deviation                   |

| IPG    | InterPacket Gap                            |

| ISI    | InterSymbol Interference                   |

| ISO    | International Standardization Organization |

| JTol   | Jitter Tolerance                           |

| LAN    | Local Area Network                         |

| LB     | Loop Bandwidth                             |

| LLC    | Logical Link Control                       |

| LMS    | Least-Mean Square                          |

| LPI    | Low Power Idle                             |

| MAC    | Media Access Control                       |

| MAN    | Metropolitan Area Network                  |

| MCB    | Module Compliance Board                    |

| MDC    | Management Data Clock                      |

| MDI    | Medium Dependent Interface                 |

| MDIO   | Management Data Input/Output               |

| MIB    | Management Information Base                |

| MII    | Media Independent Interface                |

| MIMO   | Multiple Input Multiple Output             |

| ML     | Maximum Likelihood                         |

| MLSD                        | Maximum Likelihood Sequence Detector                  |

|-----------------------------|-------------------------------------------------------|

| MLSE                        | Maximum Likelihood Sequence Estimation                |

| MMD                         | Management Data Input/Output (MDIO) Manageable Device |

| MMF                         | MultiMode Fiber                                       |

| MTTFPA                      | Mean Time To False Packet Acceptance                  |

| MUX                         | Multiplexer                                           |

| NCG                         | Net Coding Gain                                       |

| nPPI                        | n-Parallel Physical Interface                         |

| NRZ                         | Non-Return-to-Zero                                    |

| OFEC                        | Open FEC                                              |

| OMA                         | Optical Modulation Amplitude                          |

| OSI                         | Open System Interconnection                           |

| PAM4                        | 4-level Pulse Amplitude Modulation                    |

| PCS                         | Physical Coding Sublayer                              |

| PCSL                        | PCS Lane                                              |

| PD                          | PhotoDetector                                         |

| PFC                         | Priority-based Flow Control                           |

| PHY                         | Physical Layer                                        |

| PI                          | Phase Interpolator                                    |

| PLL                         | Phase Locked Loop                                     |

| PLS                         | Physical Signaling Sublayer                           |

| PMA                         | Physical Medium Attachment                            |

| PPI                         | Parallel Physical Interface                           |

| PR-PAM4                     | Partial Response PAM4                                 |

| PSD                         | Power Spectrum Density                                |

| QSFP-DD                     | Quad Small Form-Factor – Double Density               |

| RAM                         | Rapid Alignment Marker                                |

| RIN                         | Relative Intensity Noise                              |

| <b>RIN</b> <sub>x</sub> OMA | Relative Intensity Noise Optical Modulation Amplitude |

| RS                          | Reconciliation Sublayer                               |

| SD                          | Soft-Decision                                         |

| SE                          | Single-Ended                                          |

| SE-PAM4                     | Single-Ended PAM4                                     |

|                             |                                                       |

| SECQ   | Stressed Eye Closure for PAM4                   |

|--------|-------------------------------------------------|

| SER    | Symbol Error Ration                             |

| SerDes | Serializer/Deserializer                         |

| SFD    | Start Frame Delimiter                           |

| SD-FEC | Soft-Decision FEC                               |

| SMF    | Single-Mode Fiber                               |

| SMSR   | Side-Mode Suppression Ratio                     |

| SNR    | Signal to Noise Ratio                           |

| SP     | Skew Point                                      |

| SOVA   | Soft-decision Viterbi Algorith                  |

| SPC    | Single Parity Check                             |

| TDECQ  | Transmitter and Dispersion Eye Closure for PAM4 |

| TDP    | Transmitter and Dispersion Penalty              |

| TIA    | TransImpedance Amplifier                        |

| TP     | Test Point                                      |

| VECP   | Vertical Eye Closure Penalty                    |

| VCO    | Voltage-Controlled Oscillator                   |

| VMA    | Voltage Modulation Amplitude                    |

| XS     | eXtender Sublayer                               |

|        |                                                 |

#### 1 Introduction

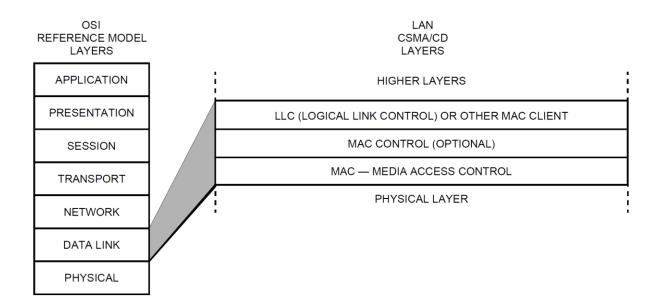

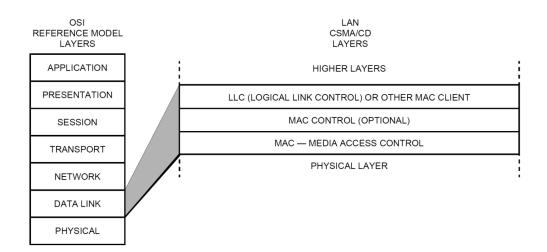

IEEE Std 802.3 is an international standard series for Local and Metropolitan Area Networks (LANs and MANs), employing Carrier Sense Multiple Access with Collision Detection (CSMA/CD) as the shared media access method, the IEEE 802.3 protocol and frame format for data communication. These international standard series is intended to encompass several media types and techniques for a variety of MAC data rates. (IEEE Std 802.3<sup>™</sup>, 2018)

IEEE 802.3 standard series defines Ethernet local area, access, and metropolitan area networks. Ethernet is specified at selected speeds of operation and uses a common MAC specification and Management Information Base (MIB). The CSMA/CD MAC protocol specifies a shared medium half duplex operation, as well as full duplex operation. Speed specific Media Independent Interfaces (MIIs) provide an architectural and optional implementation interface to selected PHY entities. The PHY encodes the frames for transmission and decodes the received frames with the modulation specified for the speed of operation, the transmission medium and the supported link length. Other specified capabilities include the control and management protocols, and the provision of power over selected twisted pair PHY types.

In 2017, IEEE published IEEE Std 802.3bs-2017 (IEEE STANDARDS ASSOCATION, 2017) which describes the general requirements for 200Gb/s and 400Gb/s Ethernet. 200 Gigabit Ethernet uses the IEEE 802.3 MAC sublayer operating at a data rate of 200Gb/s, coupled with any IEEE 802.3 200GBASE PHY implementation, and is defined for full duplex operation only. 400 Gigabit Ethernet uses the IEEE 802.3 MAC sublayer operating at a data rate of 400 Gb/s, coupled with any IEEE 802.3 400GBASE PHY implementation, and is defined for full duplex operation only. 400 Gigabit Ethernet uses the IEEE 802.3 400GBASE PHY implementation, and is defined also for full duplex operation only.

In 2018, IEEE published IEEE Std 802.3<sup>™</sup>-2018 (IEEE Std 802.3<sup>™</sup>, 2018), which describes the general requirements for starting from 10Gb/s to 400Gb/s Ethernet. For example, IEEE Std 802.3u<sup>™</sup> added 100 Mb/s operation (also called Fast Ethernet), IEEE Std 802.3z added 1000 Mb/s operation (also called Gigabit Ethernet), IEEE Std 802.3ae added 10Gb/s operation (also called 10 Gigabit Ethernet), IEEE Std 802.3ah<sup>™</sup> specified access network Ethernet (also called Ethernet in the First Mile) and IEEE Std 802.3ba added 40Gb/s operation (also called 40 Gigabit Ethernet) and

100Gb/s operation (also called 100 Gigabit Ethernet). IEEE Std 802.3<sup>™</sup>-2018 also includes the updated specifications of the IEEE Std 802.3bs-2017.

**Note:** The information provided in this study is only for academic use and not for any other purposes.

## 2 IEEE 802.3<sup>™</sup> - 2018 Ethernet Standard

#### 2.1 Media Access Control (MAC) Sublayer

The MAC sublayer defines a medium-independent capacity, based on the mediumdependent physical capacity, which provided by the PHY, and it is under the accesslayer-independent LAN LLC sublayer (or another MAC client). This is applicable to a range of local area broadcast media suitable for the media access discipline known as CSMA/CD.

The LLC and the MAC sublayers are intended to have the same functionality as that described in the OSI model for the Data Link Layer (DLL). In a broadcast network, the concept of a data link between two network entities does not correspond directly to a distinct physical connection. Nevertheless, the partitioning of functions requires two main functions generally associated with a data link control procedure to be performed in the MAC sublayer. These functions are the following:

- 1. Data encapsulation (transmit and receive)

- a. Framing (frame boundary delimitation, frame synchronization)

- b. Addressing (handling of source and destination addresses)

- c. Error detection (detection of physical medium transmission errors)

- 2. Media Access Management

- a. Medium allocation (collision avoidance)

- b. Contention resolution (collision handling)

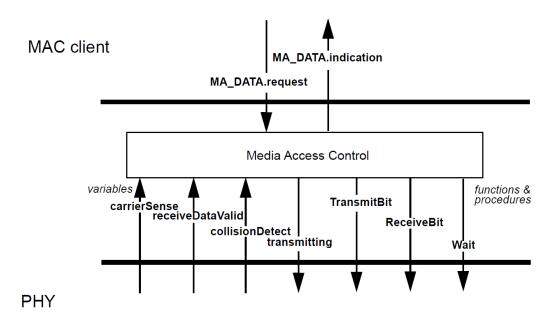

The optional MAC control sublayer, architecturally positioned between LLC (or other MAC client) and the MAC is transparent to both the underlying MAC and its client (typically LLC). The MAC sublayer operates independently of its client, e.g., it is unaware whether the client is LLC or the MAC Control sublayer. This allows the MAC to be specified and implemented, either the MAC Control sublayer is implemented or not.

IEEE 802.3<sup>™</sup> provides for two modes of operation of the MAC sublayer:

The half-duplex mode, where stations contend for the use of the physical medium, using the CSMA/CD algorithms specified. Bidirectional communication is implemented by the fast exchange of frames, rather than the full duplex operation. The half-duplex operation can be used with all supported media, and it is required with those media that are unable to support simultaneous transmission and reception without interference.

- 2. The full duplex mode of operation can be used when all the following are true:

- a. The physical medium can support simultaneous transmission and reception without interference.

- b. The physical medium between two stations on a LAN can be treated as a full duplex point-to-point link. So, when there is no contention for use of the shared medium, the multiple access (e.g., CSMA/CD) algorithms are not necessary.

- c. Both stations on the LAN are capable of and have been configured to use full duplex operation.

The most common configuration envisioned for full duplex operation consists of a switch with a dedicated LAN connecting each port to a single device.

MAC sublayer provides for real-time control and manipulation of MAC sublayer operation. MAC sublayer specifies a generalized architecture and protocol for MAC Control. The MAC Control protocol is specified such that it can support new functions to be implemented and added to IEEE 802.3<sup>™</sup> standard in the future.

Non-real-time or quasistatic control (e.g., configuration of MAC operational parameters) is provided by the layer management. The operation of the MAC Control sublayer is transparent to the CSMA/CD MAC.

#### 2.1.1 MAC Control Sublayer Architecture

The MAC control sublayer is client of the CSMA/CD MAC. *Figure 2-1* depicts the architectural positioning of the MAC Control sublayer with respect to the CSMA/CD MAC and the MAC Control client. MAC Control clients may include the Bridge Relay Entity (BRE), LLC) or other applications.

Figure 2-1. Architectural positioning of MAC Control sublayer.

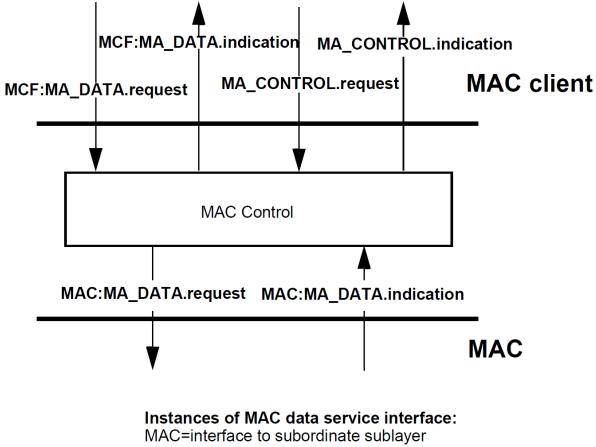

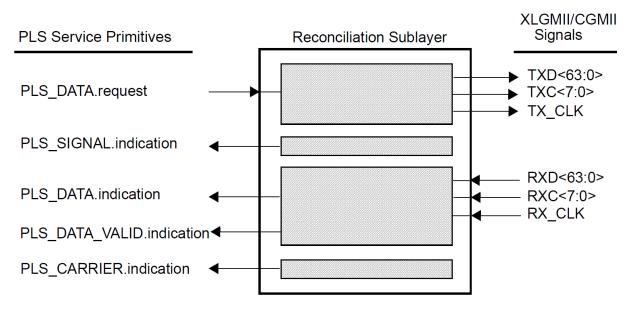

The optional MAC Control sublayer is allocated between the MAC sublayer and its MAC client. The MAC Control sublayer uses the MAC service interface to interface to the MAC client and to the MAC. **Figure 2-2** depicts the usage of interlayer interfaces by the MAC Control sublayer. Devices that implement the MAC Control sublayer shall support the MAC service primitives, *MA\_CONTROL.request* and *MA\_CONTROL.indication*.

MCF=interface to MAC client

Figure 2-2. MAC Control sublayer supports of interlayer service interfaces.

The services provided by the MAC sublayer allow the local MAC client entity to exchange LLC data with peer LLC sublayer entities.

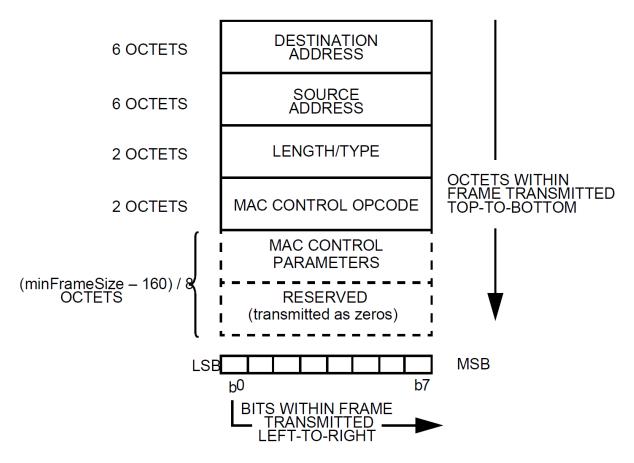

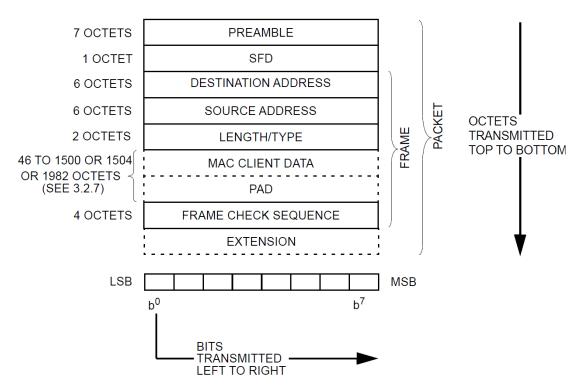

## 2.1.2 MAC Control Frame Format

MAC Control frames are fixed length, containing *minFrameSize*–32 bits. The underlying MAC prepends the Preamble and Start-of-Frame delimiter fields and appends the FCS. **Figure 2-3** depicts the MAC Control frame format.

Figure 2-3. MAC Control frame format.

The Destination Address field of the MAC Control frame contains the 48-bit address of the station(s) for which the frame is intended. It can be either an individual or a multicast (including broadcast) address. The permitted values of the Destination Address field can be specified separately for each MAC Control opcode.

The Source Address field of the MAC Control frame contains the 48-bit individual address of the station sending the frame.

The Length/Type field of the MAC Control frame is a 2-octet field that contains the hexadecimal value 88-08. This value carries the Ethertype interpretation and has been universally assigned for MAC Control of CSMA/CD LANs.

The MAC Control Opcode field contains a 2-octet operation code, which indicates the MAC Control function. It defines the semantics of the MAC Control Parameters field, which contains the list of defined MAC Control opcodes and interpretations. The MAC Control frame contains exactly one MAC Control opcode.

The MAC Control Parameters field contains the MAC Control opcode-specific parameters. This field may contain none, one, or more parameters as defined by the MAC Control Opcode. The opcode-specific semantics of the MAC Control Parameters

field specify each MAC Control function. The MAC Control Parameters field contains an integral number of octets. The length of the MAC Control Parameters field varies from a minimum of zero, to a maximum of minFrameSize - 160 bits.

The Reserved field is used only when the MAC Control parameters do not fill the fixed length MAC Control frame. The size of the Reserved field, which is optional, is determined by the size of the MAC Control Parameters field provided by the MAC Control and the minimum frame size parameter of the particular implementation. The length of Reserved field required for a MAC Control Parameters field that is n octets long is [minFrameSize – (8 × n + 160)] bits. The Reserved field is transmitted as all zeros.

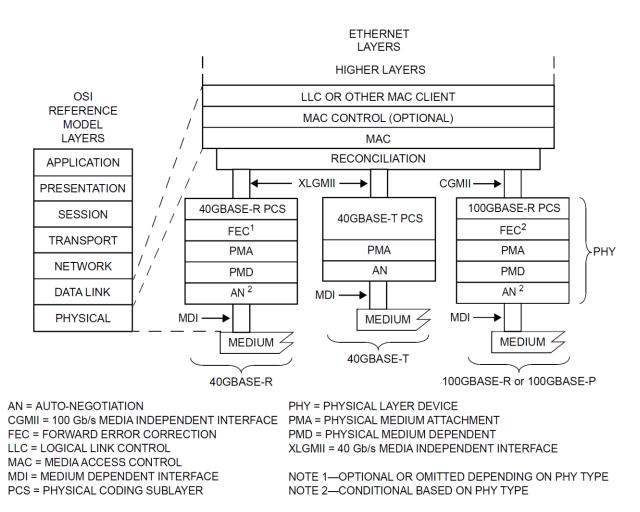

#### 2.2 Architectural Perspectives of 100Gb/s Ethernet

100 Gigabit Ethernet uses the IEEE 802.3 MAC sublayer, which operates at a data rate of 100Gb/s, coupled with any IEEE 802.3 100GBASE PHY implementation. 100Gb/s PHY entities, such as those specified in **Table 2-1**, provide a Bit Error Ratio (BER) better than or equal to 10<sup>-12</sup> at the MAC/ Physical Signaling Sublayer (PLS) service interface. 100 Gigabit Ethernet is designed for a full duplex operation only.

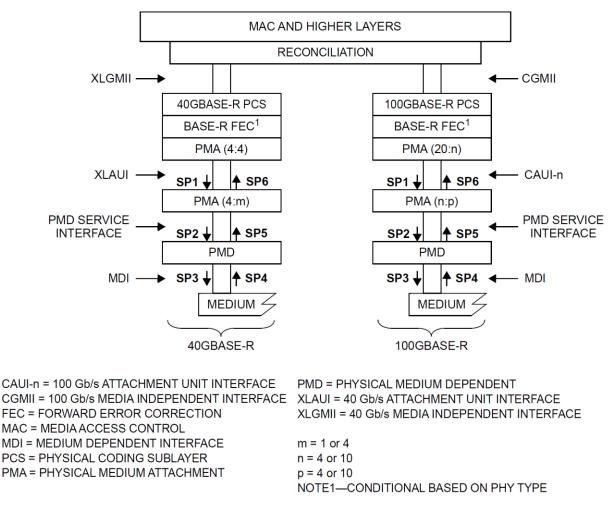

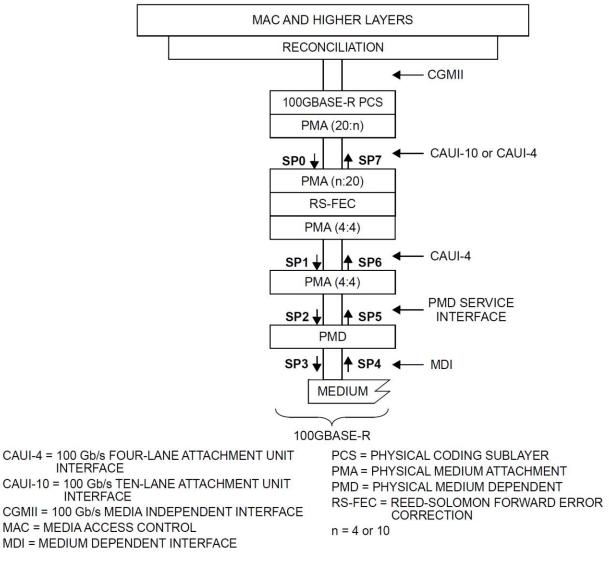

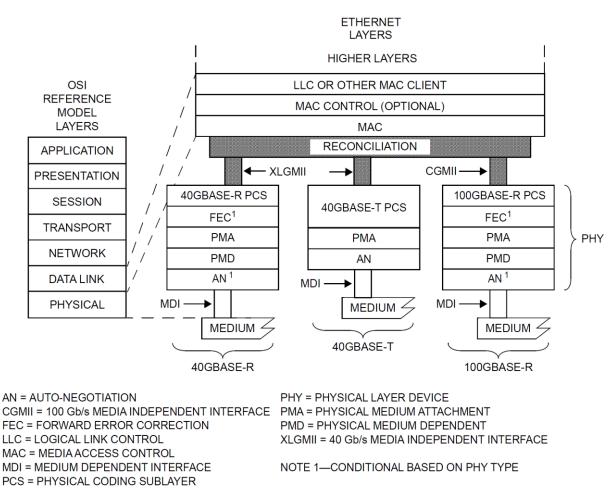

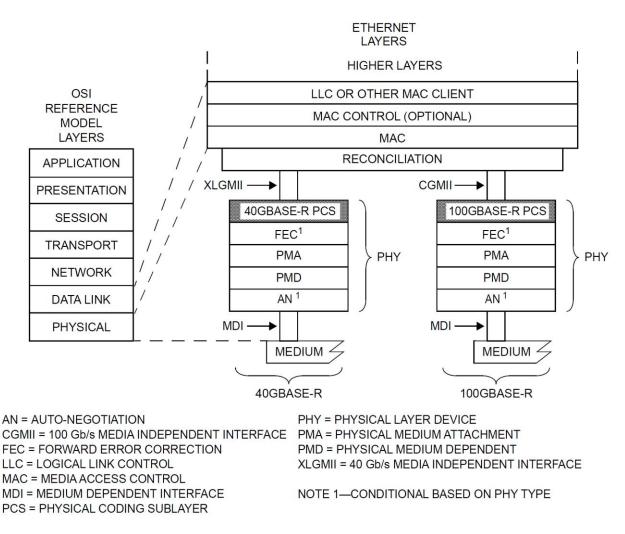

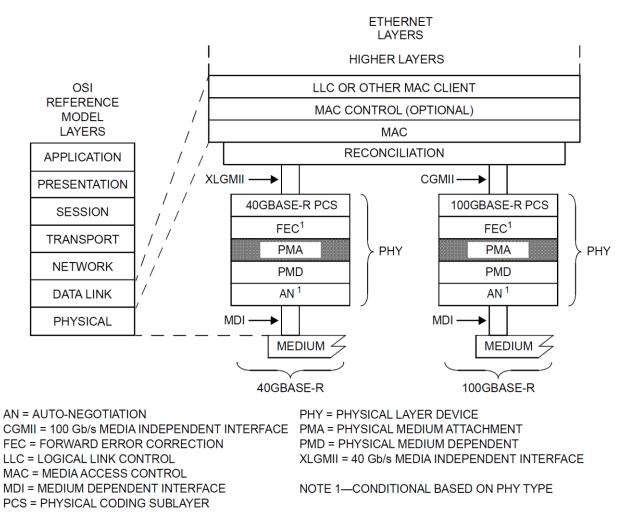

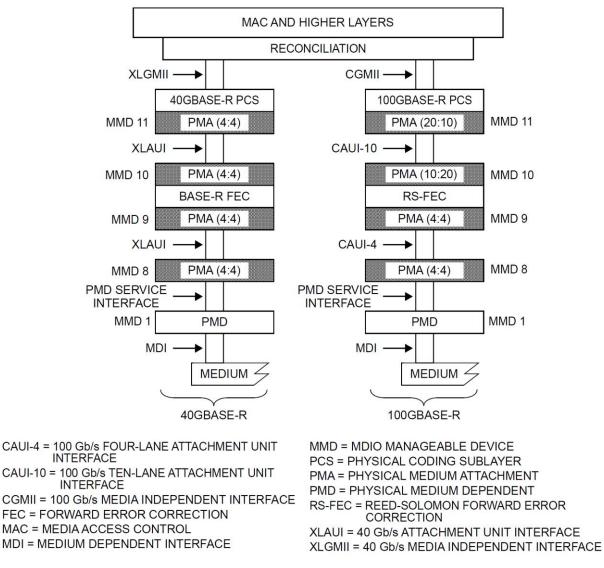

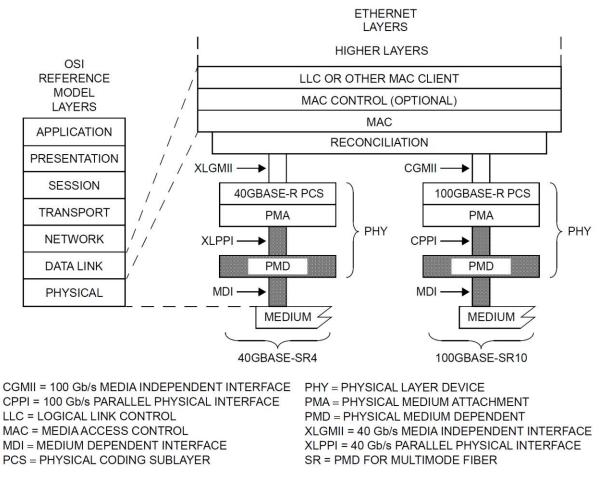

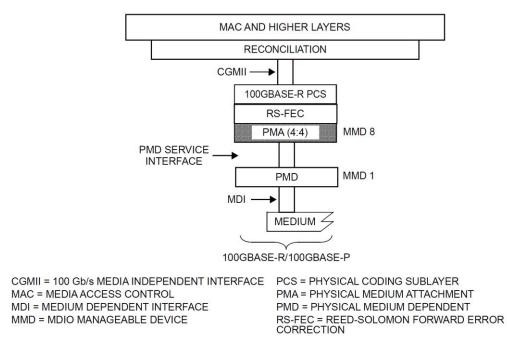

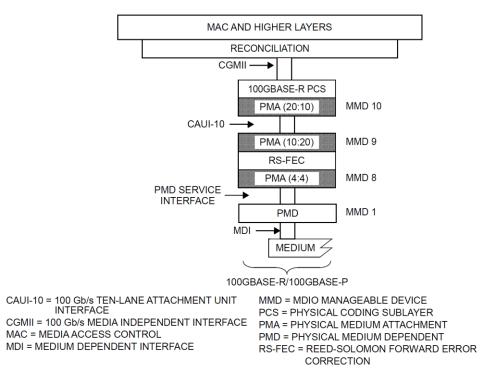

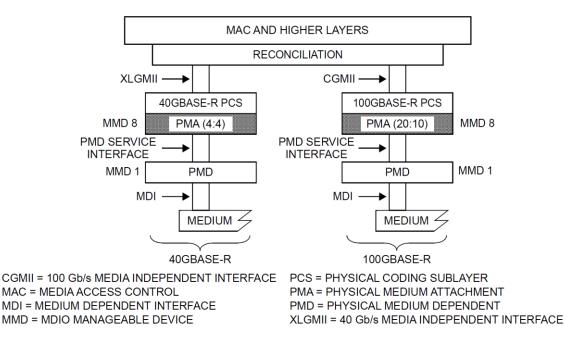

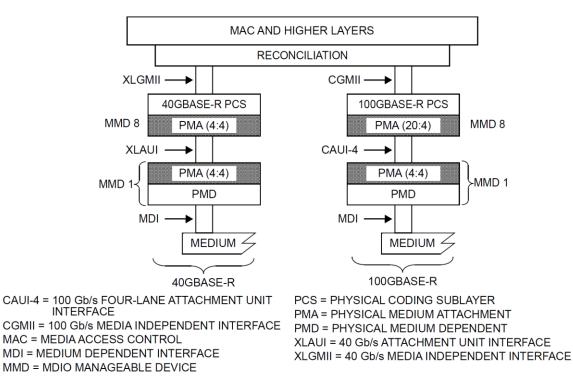

100 Gigabit Ethernet couples the IEEE 802.3 MAC to a family of 100Gb/s PHYs. The relationship among 100 Gigabit Ethernet, the IEEE 802.3 MAC, and the ISO/IEC OSI reference model are shown in **Figure 2-4**.

While this specification defines interfaces in terms of bits, octets, and frames, implementations can select another data-path width for implementation convenience. The only exceptions are as follows:

- a. The CGMII (100Gb/s Media Independent interface), which, when implemented as a logical interconnection port between the MAC sublayer and the PHY, uses a 64-bit wide data path. Physical instantiations of this interface can use another data-path width.

- b. The management interface, which, when physically implemented as the Management Data Input/Output and Management Data Clock (MDIO/MDC) at an observable interconnection port, uses a bit-wide data path.

- c. The Physical Medium Attachment (PMA) service interface, which, when physically implemented as CAUI-4 (100Gb/s four-lane Attachment Unit Interface) at an observable interconnection port, uses a 4-lane data path, as specified in Annex H, Annex I, Annex K, or Annex L.

- d. The PMA service interface, which, when physically implemented as CAUI-10 (100Gb/s ten-lane Attachment Unit Interface) at an observable interconnection port, uses a 10-lane data path as specified in Annex H or Annex I.

- e. The PMD service interface, which, when physically implemented as CPPI (100Gb/s Parallel Physical Interface) at an observable interconnection port, uses a 10-lane data path as specified in **Annex M**.

- f. The Medium Dependent Interfaces (MDIs) as specified in Section 2.7 for 100GBASE-LR4 and 100GBASE-ER4, and in Section 2.9 for 100GBASE-SR4 all use a 4-lane data path.

- g. The MDIs as specified in Section 2.6 for 100GBASE-SR10 use a 10-lane data path.

Figure 2-4. Architectural positioning of 100Gb/s Ethernet.

The nomenclature employed by the 100Gb/s PHYs is explained as follows.

The alpha-numeric prefix 100GBASE in the port type (e.g., 100GBASE-R) represents the family of PHY devices operating at the speed of 100Gb/s.

100GBASE-R represents a family of PHY devices using the Section **2.4** Physical Coding Sublayer (PCS) for 100Gb/s operation over multiple PCS lanes (see Section **2.4**) and a PMD implementing 2-level Pulse Amplitude Modulation (PAM). Some 100GBASE-R PHY devices also use the transcoding and Forward Error Correction (FEC) of Section **2.8**.

100GBASE-R represents PHY devices using the Section **2.4** PCS for 100Gb/s operation over multiple PCS lanes (see Section **2.4**) and a PMD implementing more than 2-level PAM. Some 100GBASE-P PHY devices also use the transcoding and FEC of Section **2.8**.

| Name          | Description                                                               |

|---------------|---------------------------------------------------------------------------|

| 100GBASE-SR10 | 100Gb/s PHY using 100GBASE-R encoding over ten lanes of                   |

| TOUGDAGE-ORTO | multimode fiber, with reach up to at least 100m (see Section 2.6)         |

| 100GBASE-SR4  | 100Gb/s PHY using 100GBASE-R encoding over four lanes of                  |

| 10060432-5114 | multimode fiber, with reach up to at least 100m (see Section <b>2.9</b> ) |

|               | 100Gb/s PHY using 100GBASE-R encoding over four WDM lanes                 |

| 100GBASE-LR4  | on single-mode fiber, with reach up to at least 10km (see Section         |

|               | 2.7)                                                                      |

|               | 100Gb/s PHY using 100GBASE-R encoding over four WDM lanes                 |

| 100GBASE-ER4  | on single-mode fiber, with reach up to at least 40km (see Section         |

|               | 2.7)                                                                      |

PHY devices listed in Table 2-1 are defined for operation at 100Gb/s.

Table 2-1. 100Gb/s PHYs.

## 2.2.1 Delay constraints

The predictable operation of the MAC Control *PAUSE* operation demands an upper bound on the propagation delays through the network. This implies that the MAC, the MAC Control sublayer, and the PHY implementers must conform to certain delay maxima, and the network planners and administrators conform to constraints regarding the cable topology and the concatenation of devices. **Table 2-2** depicts the values of the maximum sublayer delay (the sum of transmit and receive delays at one end of the link) in bit times, where *pause\_quanta* is the unit of measurement for the pause time specified as 512 MAC bit times as specified in **Annex G**. If the PHY contains an Auto-Negotiation sublayer, the delay of this sublayer is included within the delay of the PMD and the medium.

| Sublayer                         | Maximum<br>(bit time) | Maximum<br>(pause_quanta) | Maximum<br>(ns) | Notes                  |

|----------------------------------|-----------------------|---------------------------|-----------------|------------------------|

| 100G MAC, RS, and<br>MAC Control | 24 576                | 48                        | 245.76          |                        |

| 100GBASE-R PCS                   | 35 328                | 69                        | 353.28          |                        |

| 100GBASE-R FEC                   | 122 880               | 240                       | 1228.8          |                        |